An attempt is made to store each of the designat

ed control registers, regardless of whether the facility

requiring the presence of the control register is in

stalled.\Vhenever the storage reference causes an

access exception, the exception is indicated. The

information provided for control register positions

not associated with an installed facility is unpredicta

ble.

The second operand must be designated on a

word boundary; otherwise, a specification exception

is recognized, and the operation is suppressed.

Condition Code: The code remains unchanged.

Program Exceptions:

Privileged operation

Access (store, operand 2)

Specification

Programmiing Note

Although on someCPUs STORE CONTROL may

provide zeros in the bit positions corresponding to

the unassigned register positions, the program should

not depend on such zeros.

StoreCPU Address

STAP [S]

[ __ B_2_1_2 ________ 20 31

The processor address by which thisCPU is identi

fied in a multiprocessing system is stored at the half

word location designated by the second-operand

address.

The operand must be designated on a halfword

boundary; otherwise, a specifIcation exception is

recognized, and the operation is suppressed. The

operation :is suppressed on protection and. addressing

exceptions.

Condition Code: The code remains unchanged.

Program Exceptions:Operation (if the multiprocessing feature is no; installed)

Privileged operation

Access (store; operand 2)

Specification

112System/370 Principles of Operation

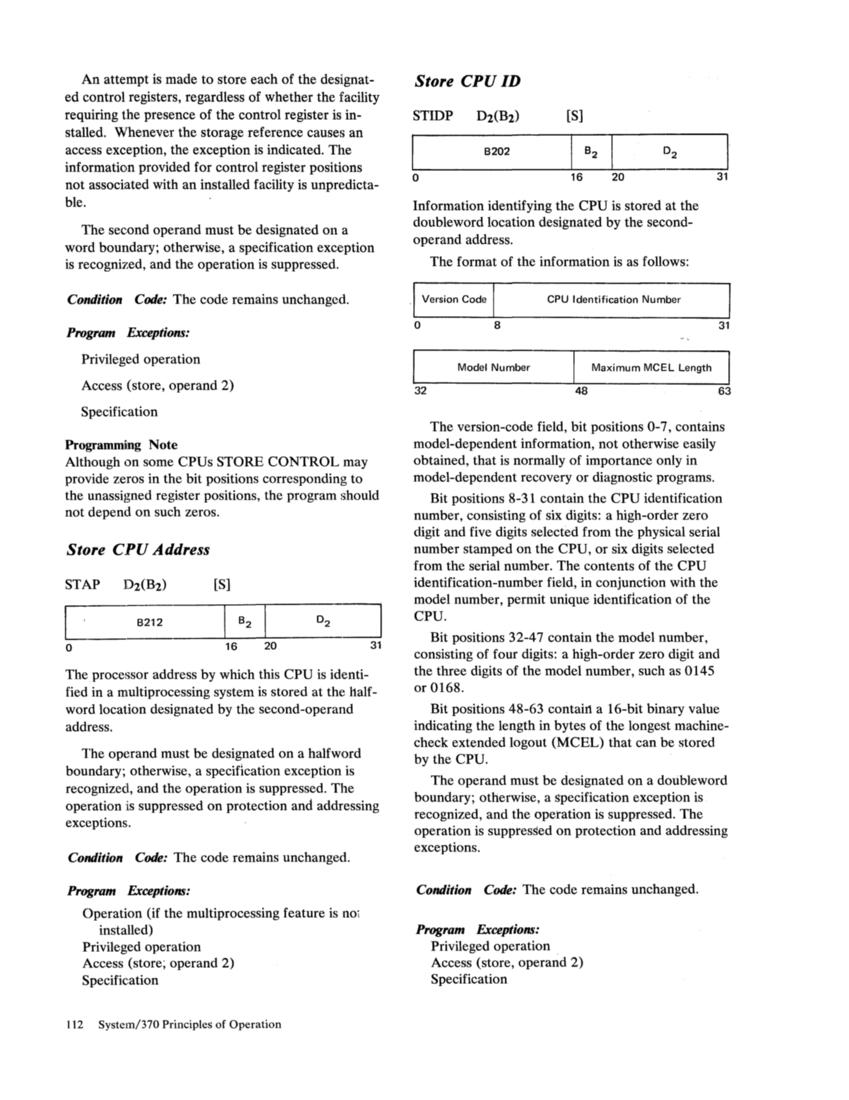

Store CPU ID

STIDP [S]B202 o 16 20 Information identifying the CPU is stored at the

doubleword location designated by the second

operand address.

The format of the information is as follows:

VersionCode CPU Identification Number

o 8

31

31Model Number Maximum MeEL Length I 32 48 63

The version-code field, bit positions0-7, contains

model-dependent information, not otherwise easily

obtained, that is normally of importance only in

model-dependent recovery or diagnostic programs.

Bit positions 8-31 contain theCPU identification

number, consisting of six digits: a high-order zero

digit and five digits selected from the physical serial

number stamped on theCPU, or six digits selected

from the serial number. The contents of theCPU identification-number field, in conjunction with the

model number, permit unique identification of theCPU. Bit positions 32-47 contain the model number,

consisting of four digits: a high-order zero digit and

the three digits of the model number, such as0145 or 0168. Bit positions 48-63 contairt a 16-bit binary value

indicating the length in bytes of the longest machine

check extended logout (MCEL) that can be stored

by theCPU. The operand must be designated on a dotibleword

boundary; otherwise, a specification exception is

recognized, and the operation is suppressed. The

operation is suppressed on protection and addressing

exceptions.

Condition Code: The code remains unchanged.

Program Exceptions:

Privileged operation. Access (store, operand 2)

Specification

ed control registers, regardless of whether the facility

requiring the presence of the control register is in

stalled.

access exception, the exception is indicated. The

information provided for control register positions

not associated with an installed facility is unpredicta

ble.

The second operand must be designated on a

word boundary; otherwise, a specification exception

is recognized, and the operation is suppressed.

Condition Code: The code remains unchanged.

Program Exceptions:

Privileged operation

Access (store, operand 2)

Specification

Programmiing Note

Although on some

provide zeros in the bit positions corresponding to

the unassigned register positions, the program should

not depend on such zeros.

Store

STAP [S]

[ __ B_2_1_2 ______

The processor address by which this

fied in a multiprocessing system is stored at the half

word location designated by the second-operand

address.

The operand must be designated on a halfword

boundary; otherwise, a specifIcation exception is

recognized, and the operation is suppressed. The

operation :is suppressed on protection and. addressing

exceptions.

Condition Code: The code remains unchanged.

Program Exceptions:

Privileged operation

Access (store; operand 2)

Specification

112

Store CPU ID

STIDP [S]

doubleword location designated by the second

operand address.

The format of the information is as follows:

Version

o 8

31

31

The version-code field, bit positions

model-dependent information, not otherwise easily

obtained, that is normally of importance only in

model-dependent recovery or diagnostic programs.

Bit positions 8-31 contain the

number, consisting of six digits: a high-order zero

digit and five digits selected from the physical serial

number stamped on the

from the serial number. The contents of the

model number, permit unique identification of the

consisting of four digits: a high-order zero digit and

the three digits of the model number, such as

indicating the length in bytes of the longest machine

check extended logout (MCEL) that can be stored

by the

boundary; otherwise, a specification exception is

recognized, and the operation is suppressed. The

operation is suppressed on protection and addressing

exceptions.

Condition Code: The code remains unchanged.

Program Exceptions:

Privileged operation

Specification