may be necessary that a program, which is not aware

of the present status, disable program-event record

ing for a few instructions.

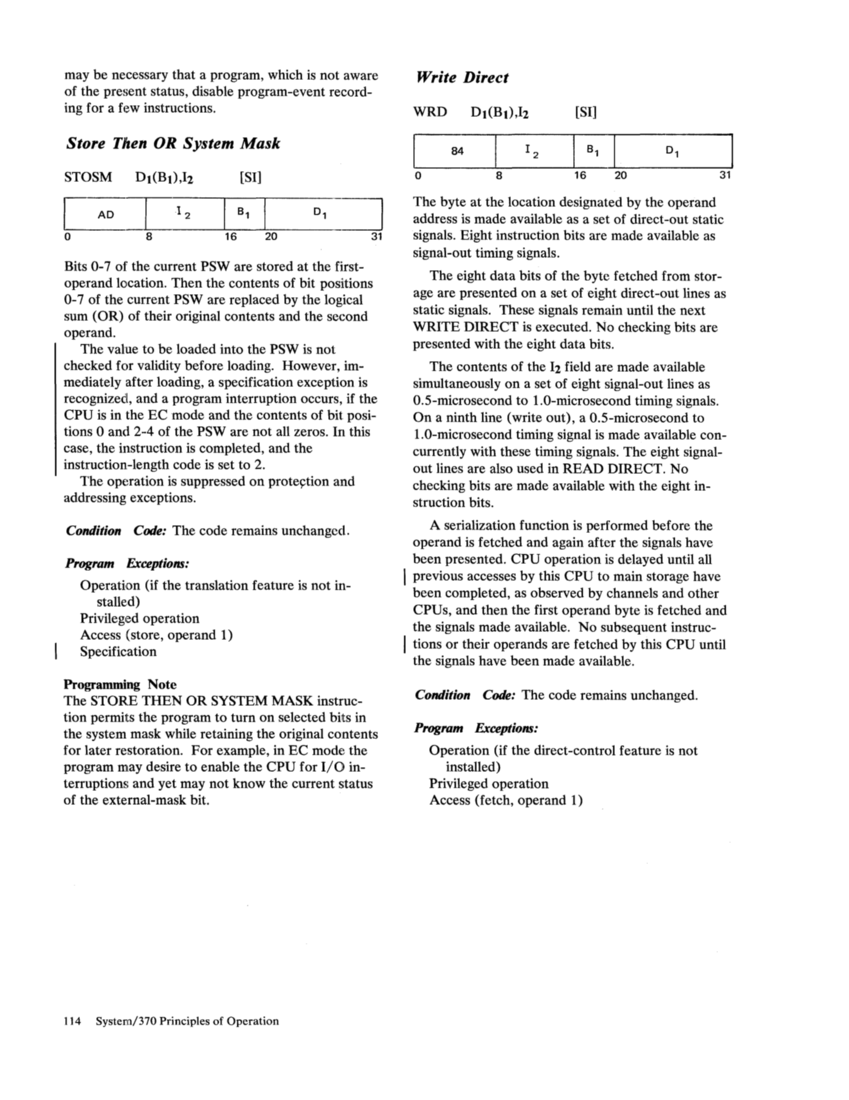

Store ThenOR System Mask STOSM [SI] ------,----S, ""::-::--1 _D 1 . :=J o 8 16 20 31

Bits0-7 of the current PSW are stored at the first

operand location. Then the contents of bit positions0- 7 of the current PSW are replaced by the logical

sum(OR) of their original contents and the second

operand.

The value to be loaded into thePSW is not

checked for validity before loading. However, im

mediately after loading, a specification exception is

recognized, and a program interruption occurs, if theCPU is in the EC mode and the contents of bit posi

tions0 and 2-4 of the PSW are not all zeros. In this

case, the instruction is completed, and the

instruction-length code is set to 2.

Theoperation is suppressed on prote9tion and

addressing exceptions.

Condition Code: The code remains unchangcd.

Program Exceptions:

Operation (if the translation feature is not in-

stalled)Privileged operation

Access (store, operand 1)

Specification

Programming Note

TheSTORE THEN OR SYSTEM MASK instruc

tion permits the program to turn on selected bits in

the system mask while retaining the original contents

for later restoration. For example, in ECmode the

program may desire to enable theCPU for I/O in

terruptions and yet may not know the current status

of the external-mask bit.

114 System/370 Principles of Operation

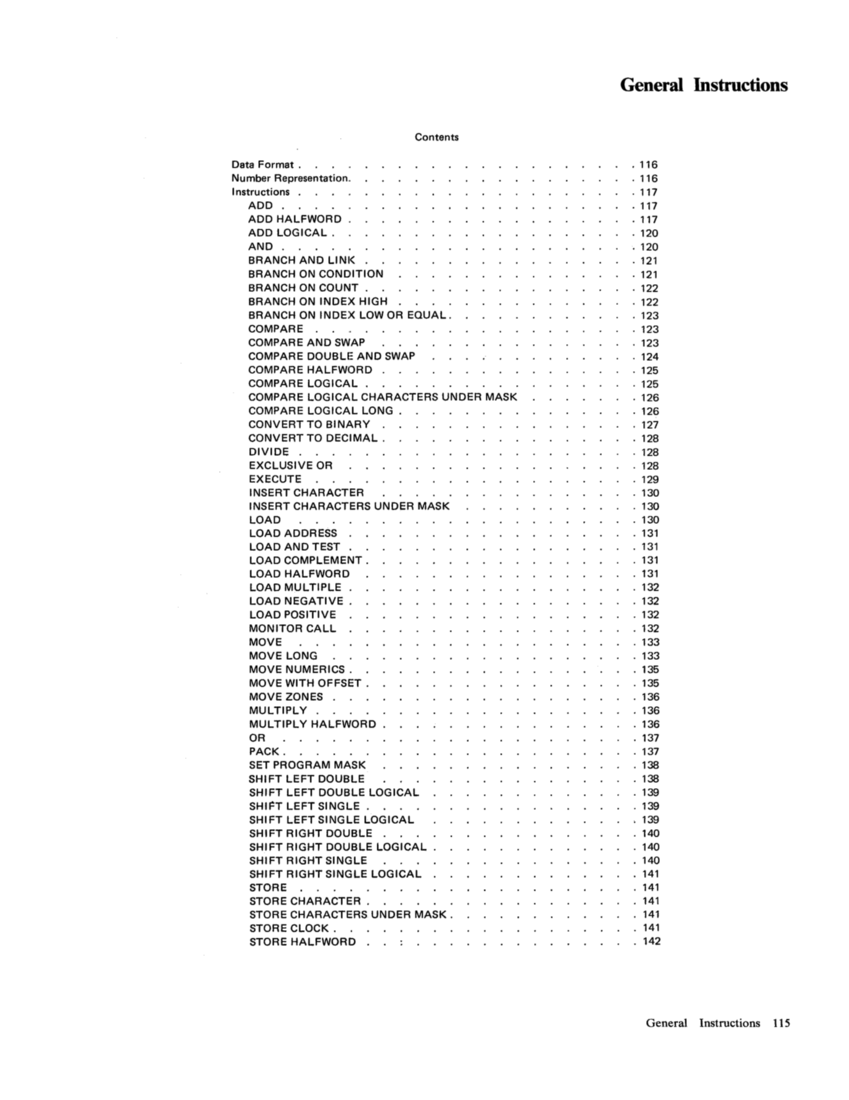

Write Direct

WRD Dt (Bt),I2 [SI]

84 I2I B, I D, 0 8 16 20 31

The byte at the location designated by the operand

address is made available as a set of direct-out static

signals. Eight instruction bits are made available as

signal-out timing signals.

The eight data bits of the bytc fetched from stor

age are presented on a set of eight direct-out lines as

static signals. These signals remain until the next

WRITE DIRECT is executed. No checking bits are

presented with the eight data bits.

The contents of theh field are made available

simultaneously on a set of eight signal-out lines as

0.5-microsecond to 1.0-microsecond timing signals.On a ninth line (write out), a 0.5-microsecond to

1.0-microsecond timing signal is made available con

currently with these timing signals. The eight signal

out lines are also used in READ DIRECT. No

checking bits are made available with the eight in

struction bits.

A serialization function is performed before the

operand is fetched and again after the signals have

been presented.CPU operation is delayed until all I previous accesses by this CPU to main storage have

been completed, as observed by channels and otherCPUs, and then the first operand byte is fetched and

the signals made available. No subsequent instruc-I tions or their operands are fetched by this CPU until

the signals have been made available.

Condition Code: The code remains unchanged.Program Exceptions:

Operation (if the direct-control feature is not

installed)

Privileged operation

Access (fetch, operand 1)I

of the present status, disable program-event record

ing for a few instructions.

Store Then

Bits

operand location. Then the contents of bit positions

sum

operand.

The value to be loaded into the

checked for validity before loading. However, im

mediately after loading, a specification exception is

recognized, and a program interruption occurs, if the

tions

case, the instruction is completed, and the

instruction-length code is set to 2.

The

addressing exceptions.

Condition Code: The code remains unchangcd.

Program Exceptions:

Operation (if the translation feature is not in-

stalled)

Access (store, operand 1)

Specification

Programming Note

The

tion permits the program to turn on selected bits in

the system mask while retaining the original contents

for later restoration. For example, in EC

program may desire to enable the

terruptions and yet may not know the current status

of the external-mask bit.

114 System/370 Principles of Operation

Write Direct

WRD Dt (Bt),I2 [SI]

84 I2

The byte at the location designated by the operand

address is made available as a set of direct-out static

signals. Eight instruction bits are made available as

signal-out timing signals.

The eight data bits of the bytc fetched from stor

age are presented on a set of eight direct-out lines as

static signals. These signals remain until the next

WRITE DIRECT is executed. No checking bits are

presented with the eight data bits.

The contents of the

simultaneously on a set of eight signal-out lines as

0.5-microsecond to 1.0-microsecond timing signals.

1.0-microsecond timing signal is made available con

currently with these timing signals. The eight signal

out lines are also used in READ DIRECT. No

checking bits are made available with the eight in

struction bits.

A serialization function is performed before the

operand is fetched and again after the signals have

been presented.

been completed, as observed by channels and other

the signals made available. No subsequent instruc-

the signals have been made available.

Condition Code: The code remains unchanged.

Operation (if the direct-control feature is not

installed)

Privileged operation

Access (fetch, operand 1)