one's complement of a number is obtained by invert

ing each bit of the number.

In an arithmetic operation, acarry out of the in

teger field changes the sign. However, in algebraic

left-shifting the sign bit does not change even if sig

nificant high-order bits are shifted out.

Programming Note

The integer part of a signed fixed-point number may

be considered to represent a positive value, with the

sign representing a value of either zero or the maxi

mum negative number.

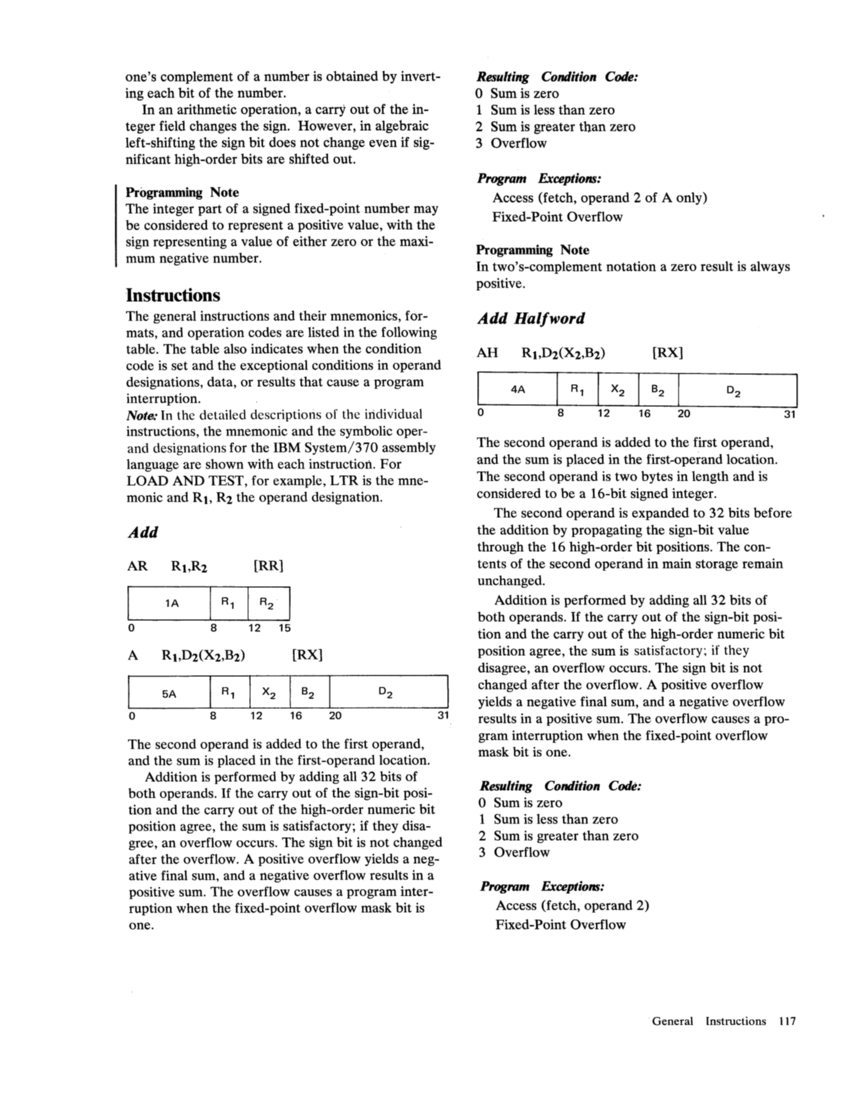

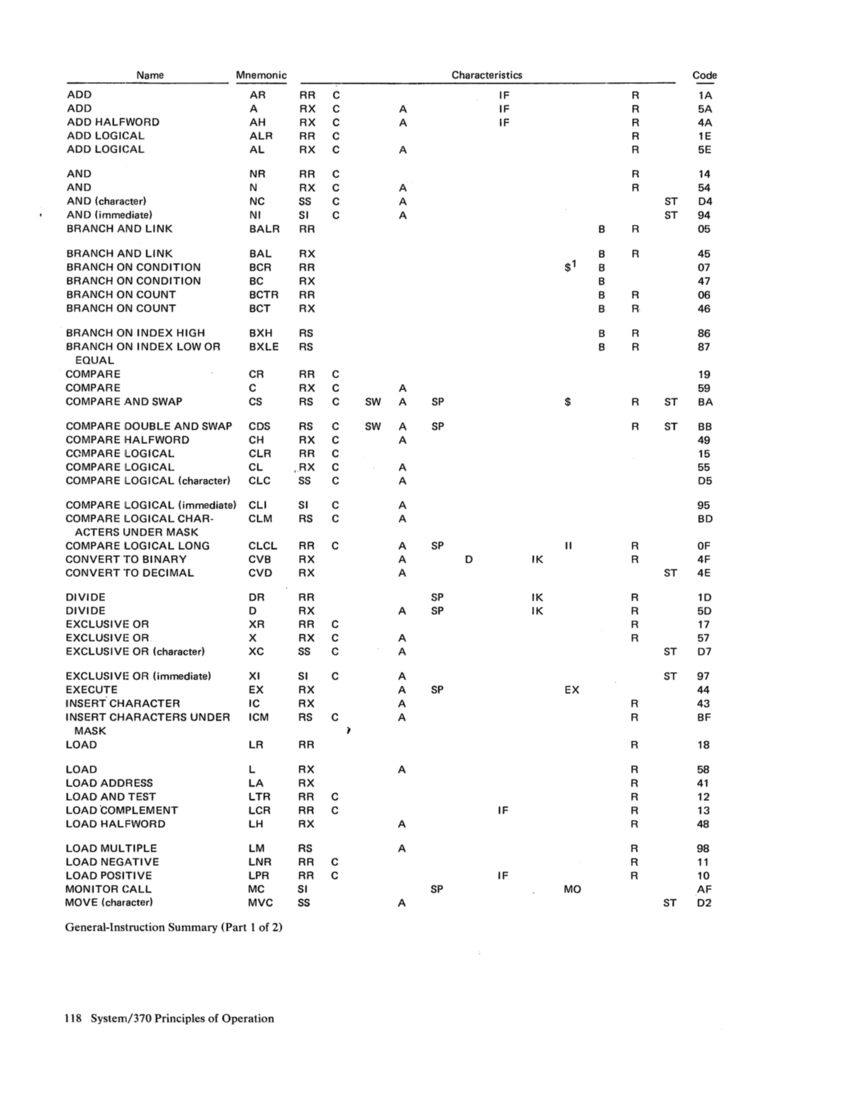

Instructions

The general instructions and their mnemonics, for

mats, and operation codes are listed in the following

table. The table also indicates when the condition

code is set and the exceptional conditions in operand

designations, data, or results that cause a program

interruption.

Note: In the detailed descriptions of the individual

instructions, the mnemonic and the symbolic oper

andSystem/370 assembly

language are shown with each instruction. ForLOAD AND TEST, for example, LTR is the mne

monic and R 1, R2 the operand designation.

Add

AR [RR]

o 8 12 15

A [RX]

5A

o 8 12 1620 The second operand is added to the first operand,

and the sum is placed in the first-operand location.

31

Addition is performed by adding all 32 bits of

both operands. If the carry out of the sign-bit posi

tion and the carry out of the high-order numeric bit

position agree, the sum is satisfactory; if they disa

gree, an overflow occurs. The sign bit is not changed

after the overflow. A positive overflow yields a neg

ative final sum, and a negative overflow results in a

positive sum. The overflow causes a program inter

ruption when the fixed-point overflow mask bit is

one.

Resulting Condition Code:

oSum is zero

1Sum is less than zero

2Sum is greater than zero

3 Overflow

Program Exceptions:

Access (fetch, operand 2 of A only)

Fixed-Point Overflow

Programming Note

In two's-complement notation a zero result is always

positive.

Add Hal/word

AH [RX]

4A

o 8 12 1620 The second operand is added to the first operand,

and the sum is placed in the first-operand location.

The second operand is two bytes in length and is

considered to be a 16-bit signed integer.

31

The second operand is expanded to 32 bits before

the addition by propagating the sign-bit value

through the 16 high-order bit positions. The con

tents of the second operand in main storage remain

unchanged.

Addition is performed by adding all 32 bits of

both operands. If the carry out of the sign-bit posi

tion and the carry out of the high-order numeric bit

position agree, the sum is satisfactory; if they

disagree, an overflow occurs. The sign bit is not

changed after the overflow. A positive overflow

yields a negative final sum, and a negative overflow

results in a positive sum. The overflow causes a pro

gram interruption when the fixed-point overflow

mask bit is one.

Resulting ConditionCode: o Sum is zero

1Sum is less than zero

2Sum is greater than zero

3 Overflow

Program Exceptions:

Access (fetch, operand 2)

Fixed-Point Overflow

General Instructions 117

ing each bit of the number.

In an arithmetic operation, a

teger field changes the sign. However, in algebraic

left-shifting the sign bit does not change even if sig

nificant high-order bits are shifted out.

Programming Note

The integer part of a signed fixed-point number may

be considered to represent a positive value, with the

sign representing a value of either zero or the maxi

mum negative number.

Instructions

The general instructions and their mnemonics, for

mats, and operation codes are listed in the following

table. The table also indicates when the condition

code is set and the exceptional conditions in operand

designations, data, or results that cause a program

interruption.

Note: In the detailed descriptions of the individual

instructions, the mnemonic and the symbolic oper

and

language are shown with each instruction. For

monic and R 1, R2 the operand designation.

Add

AR [RR]

o 8 12 15

A [RX]

5A

o 8 12 16

and the sum is placed in the first-operand location.

31

Addition is performed by adding all 32 bits of

both operands. If the carry out of the sign-bit posi

tion and the carry out of the high-order numeric bit

position agree, the sum is satisfactory; if they disa

gree, an overflow occurs. The sign bit is not changed

after the overflow. A positive overflow yields a neg

ative final sum, and a negative overflow results in a

positive sum. The overflow causes a program inter

ruption when the fixed-point overflow mask bit is

one.

Resulting Condition Code:

o

1

2

3 Overflow

Program Exceptions:

Access (fetch, operand 2 of A only)

Fixed-Point Overflow

Programming Note

In two's-complement notation a zero result is always

positive.

Add Hal/word

AH [RX]

4A

o 8 12 16

and the sum is placed in the first-operand location.

The second operand is two bytes in length and is

considered to be a 16-bit signed integer.

31

The second operand is expanded to 32 bits before

the addition by propagating the sign-bit value

through the 16 high-order bit positions. The con

tents of the second operand in main storage remain

unchanged.

Addition is performed by adding all 32 bits of

both operands. If the carry out of the sign-bit posi

tion and the carry out of the high-order numeric bit

position agree, the sum is satisfactory; if they

disagree, an overflow occurs. The sign bit is not

changed after the overflow. A positive overflow

yields a negative final sum, and a negative overflow

results in a positive sum. The overflow causes a pro

gram interruption when the fixed-point overflow

mask bit is one.

Resulting Condition

1

2

3 Overflow

Program Exceptions:

Access (fetch, operand 2)

Fixed-Point Overflow

General Instructions 117