ing storage. Clearing can be accomplished by setting

the padding character to zero and the second oper

:and count to zero.

When the first-operand count is zero, the opera

tion consists in setting the condition code and setting

the high-order bytes of registers Rl and R2 to zero.

When the contents of the R 1 and R2 fields are the

same, the operation proceeds the same way as when

two distinct pairs of registers having the same con

tents are specified. Condition code

tection and addressing exceptions are indicated when

called for by the operand designation.

Since the execution of

tible, the instruction cannot be used for situations

where the program must rely on uninterrupted exe

cution of the instruction or on

being updated during the execution of the instruc

tion. Similarly, the program should normally not let

the first operand of

tion of the instruction since the new contents of the

location may be interpreted for a resumption after

an interruption, or if the instruction is ref etched

without an interruption.

Special precautions must be taken if

programming notes under EXECUTE.

When the stop key is activated during the execu

tion of

completion of the execution of the next unit of oper

ation. Similarly, in the instruction-step mode, only a

unit of operation is performed. The amount of data

processed in a unit of operation depends on the

model and may depend on the particular condition

that causes the execution of the instruction to be

interrupted.

Move Numerics

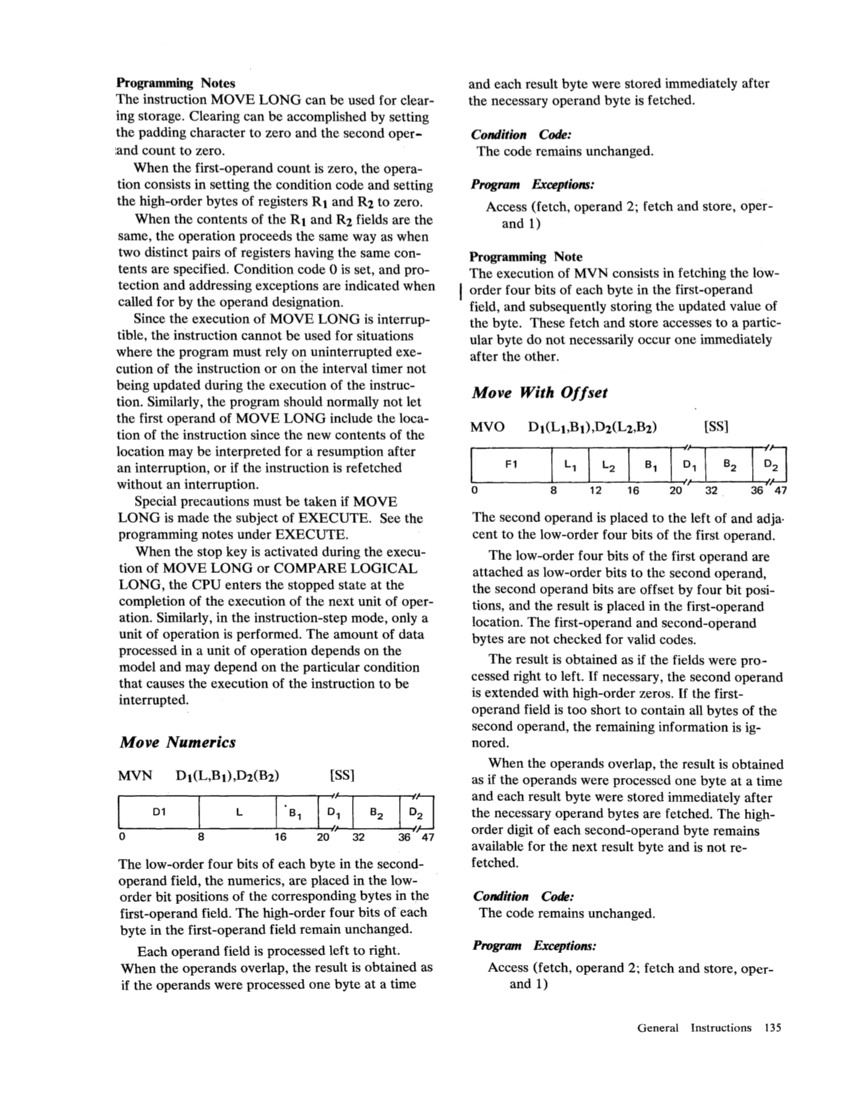

MVN [SS]

The low-order four bits of each byte in the second

operand field, the numerics, are placed in the low

order bit positions of the corresponding bytes in the

first-operand field. The high-order four bits

byte in the first-operand field remain unchanged.

Each operand field is processed left to right.

When the operands overlap, the result is obtained as

if the operands were processed one byte at a time

and each result byte were stored immediately after

the necessary operand byte is fetched.

Condition Code:

The code remains unchanged.

Program

and 1)

Programming

field, and subsequently storing the updated value of

the byte. These fetch and store accesses to a partic

ular byte do not necessarily occur one immediately

after the other.

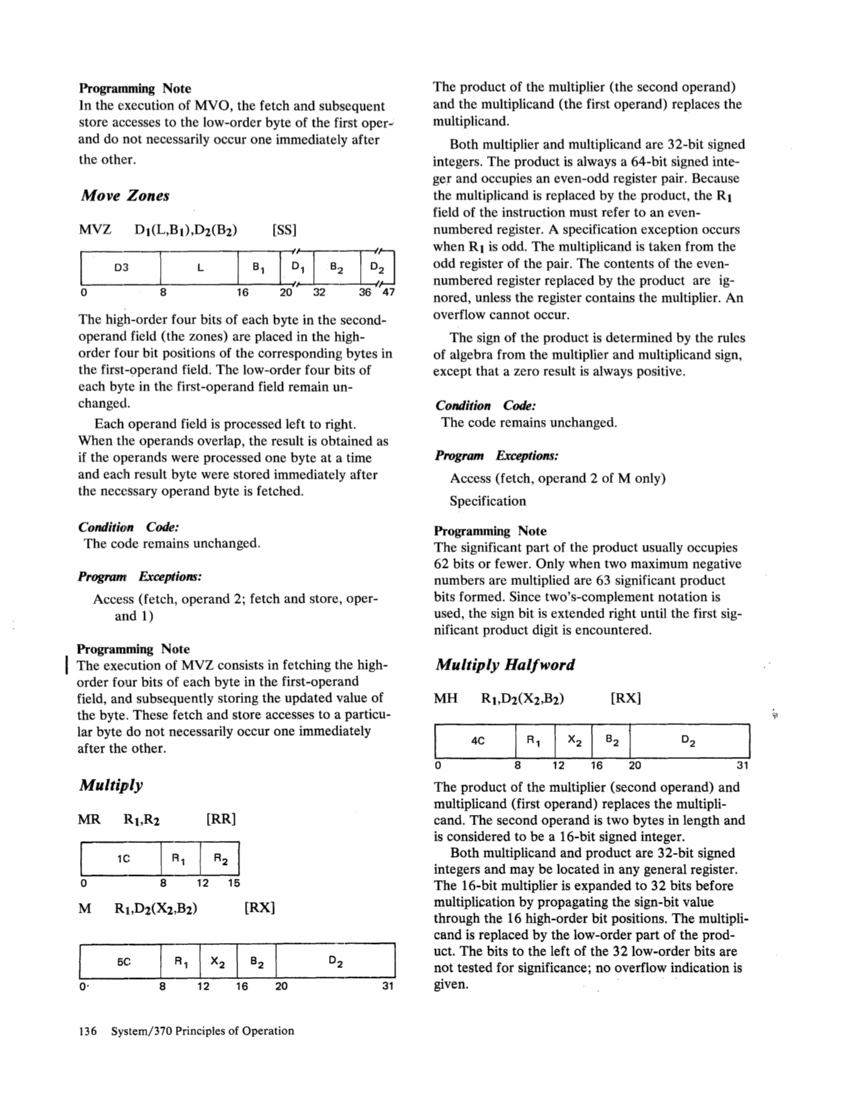

Move With Offset

F1

The second operand is placed to the left of and

The low-order four bits of the first operand are

attached as low-order bits to the second operand,

the second operand bits are offset by four bit posi

tions, and the result is placed in the first-operand

location. The first-operand and second-operand

bytes are not checked for valid codes.

The result is obtained as if the fields were pro

cessed right to left. If necessary, the second operand

is extended with high-order zeros. If the first

operand field is too short to contain all bytes of the

second operand, the remaining information is ig

nored.

When the operands overlap, the result is obtained

as if the operands were processed one byte at a time

and each result byte were stored immediately after

the necessary operand bytes are fetched. The high

order digit of each second-operand byte remains

available for the next result bytc and is not rc

fetched.

Condition Code:

The code remains unchanged.

Program Exceptions:

Access (fetch, operand

and 1)

General Instructions 135