Programming Note

In the execution ofMVO, the fetch and subsequent

storeaecesses to the low-order byte of the first oper-'

and do not necessarily occur one immediately after

the other.

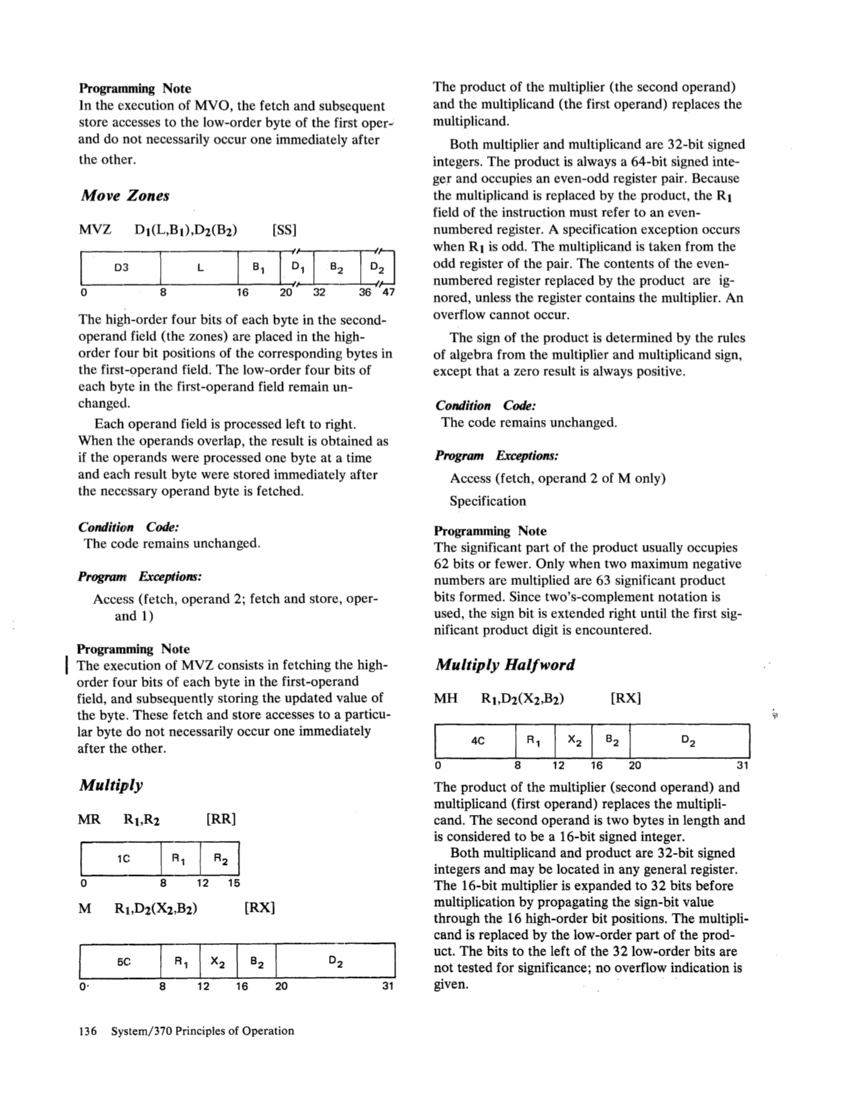

Move ZonesB, 20 32 36 47

The high-order four bits of each byte in thesecond operand field (the zones) are placed in the high order four bit positions of the corresponding bytes in

the first-operand field. The low-order four bits of

each byte in the first-operand field remainun changed.

Each operand field is processed left to right.

When the operands overlap, the result is obtained as

if the operands were processed one byte at a time

and each result byte were stored immediately after

thenecessary operand byte is fetched. Condition Code:

The code remains unchanged.

Program Exceptions:

Access (fetch, operand 2; fetch and store,oper and 1)

Programming Note

The execution of MVZ consists in fetching thehigh order four bits of each byte in the first-operand

field, and subsequently storing the updated value of

the byte. These fetch and store accesses to aparticu lar byte do not necessarily occur one immediately

after the other.

MUltiply

MR Rl,R2 [RR]

136System/370 Principles of Operation The product of the multiplier (the second operand)

and the multiplicand (the first operand) replaces the

mUltiplicand.

Both mUltiplier and multiplicand are 32-bit signed

integers. The product is always a 64-bit signedinte ger and occupies an even-odd register pair. Because

the multiplicand is replaced by the product, the R 1

field of the instruction must refer to aneven numbered register. A specification exception occurs

when R

1 is odd. The multiplicand is taken from the

odd register of the pair. The contents of theeven numbered register replaced by the product are ig nored, unless the register contains the multiplier. An

overflow cannot occur.

The sign of the product is determined by the rules

of algebra from the multiplier and multiplicand sign,

except that a zero result is always positive.

Condition Code:

The code remains unchanged.

Program Exceptions:

Access (fetch, operand 2 of M only)

Specification

Programming Note

The significant part of the product usually occupies

62 bits or fewer.Only when two maximum negative

numbers are multiplied are 63 significant product

bits formed. Since two's-complement notation is

used, the sign bit is extended right until the firstsig nificant product digit is encountered.

Multiply Hal/word

MH Rl,D2(X2,B2) [RX]

4C

o 8 12 1620 31

The product of the multiplier (second operand) and

multiplicand (first operand) replaces themultipli cand. The second operand is two bytes in length and

is considered to be a 16-bit signed integer.

Both multiplicand and product are 32-bit signed

integers and may be located in any general register.

The 16-bit multiplier is expanded to 32 bits before

multiplication by propagating thesign-bit value

through the 16 high-order bit positions. The multipli

cand is replaced by the low-order part of the prod

uct. The bits to the left of the 32 low-order bits are

not tested for significance; no overflow indication is

given.

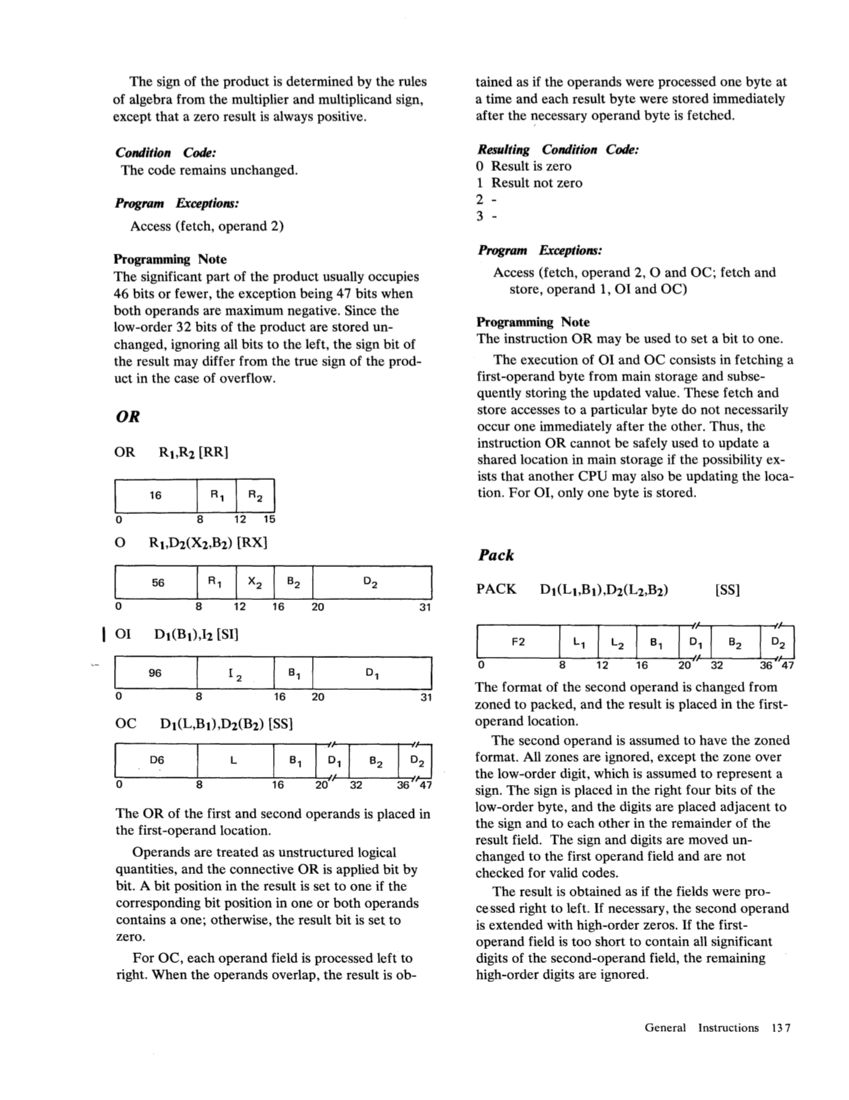

In the execution of

store

and do not necessarily occur one immediately after

the other.

Move Zones

The high-order four bits of each byte in the

the first-operand field. The low-order four bits of

each byte in the first-operand field remain

Each operand field is processed left to right.

When the operands overlap, the result is obtained as

if the operands were processed one byte at a time

and each result byte were stored immediately after

the

The code remains unchanged.

Program Exceptions:

Access (fetch, operand 2; fetch and store,

Programming Note

The execution of MVZ consists in fetching the

field, and subsequently storing the updated value of

the byte. These fetch and store accesses to a

after the other.

MUltiply

MR Rl,R2 [RR]

136

and the multiplicand (the first operand) replaces the

mUltiplicand.

Both mUltiplier and multiplicand are 32-bit signed

integers. The product is always a 64-bit signed

the multiplicand is replaced by the product, the R 1

field of the instruction must refer to an

when R

1 is odd. The multiplicand is taken from the

odd register of the pair. The contents of the

overflow cannot occur.

The sign of the product is determined by the rules

of algebra from the multiplier and multiplicand sign,

except that a zero result is always positive.

Condition Code:

The code remains unchanged.

Program Exceptions:

Access (fetch, operand 2 of M only)

Specification

Programming Note

The significant part of the product usually occupies

62 bits or fewer.

numbers are multiplied are 63 significant product

bits formed. Since two's-complement notation is

used, the sign bit is extended right until the first

Multiply Hal/word

MH Rl,D2(X2,B2) [RX]

4C

o 8 12 16

The product of the multiplier (second operand) and

multiplicand (first operand) replaces the

is considered to be a 16-bit signed integer.

Both multiplicand and product are 32-bit signed

integers and may be located in any general register.

The 16-bit multiplier is expanded to 32 bits before

multiplication by propagating the

through the 16 high-order bit positions. The multipli

cand is replaced by the low-order part of the prod

uct. The bits to the left of the 32 low-order bits are

not tested for significance; no overflow indication is

given.