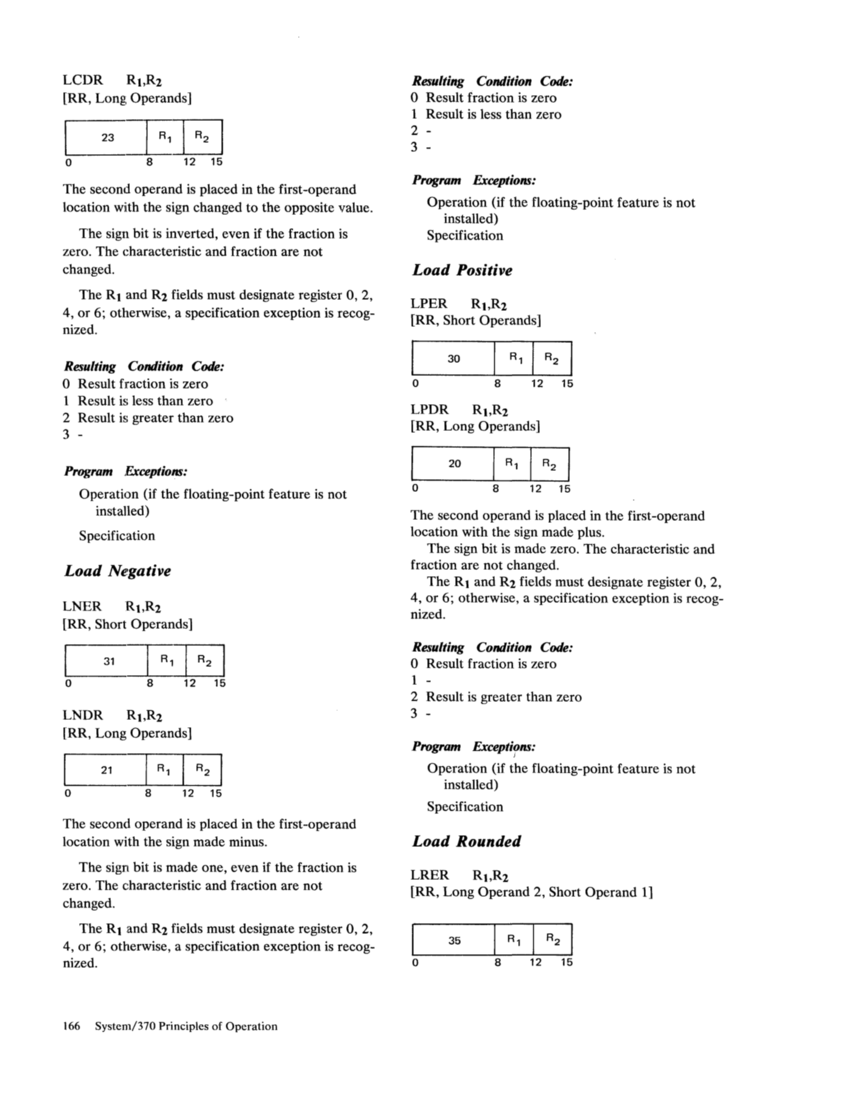

LCDR Rl,R2

[RR, LongOperands] The second operand is placed in the first-operand

locationwith the sign changed to the opposite value.

The sign bit is inverted, even if the fraction is

zero. Theeharacteristic and fraction are not

changed.

The Rl and R2 fields must designate register0, 2,

4, or6; otherwise, a specification exception is recog

nized.

Resulting Condition Code:° Result fraction is zero

1 Resultis less than zero

2 Resultis greater than zero

3 -

ProgramExceptions: Operation (if the floating-point feature is not

installed)

Specification

Load Negative

LNER Rl,R2

[RR,Short Operands] LNDR Rl,R2

[RR, LongOperands] o 8 12 15

The second operand is placed in the first-operand

location with the sign made minus.

The sign bit is made one, even if the fraction is

zero. The characteristic and fraction are not

changed.

The Rl and R2 fields must designate register0, 2,

4, or6; otherwise, a specification exception is recog

nized.

166System/370 Principles of Operation Resulting Condition Code: ° Result fraction is zero

1 Result is less than zero

2 -

3 -

Program Exceptions:Operation (if the floating-point feature is not

installed)

Specification

Load PositiveLPER Rl,R2

[RR,Short Operands] 30 o 8 12 15 LPDR Rl,R2

[RR, LongOperands] 20 o 8 12 15

The second operand is placed in the first-operand

location with the sign made plus.

The sign bit is made zero. The characteristic and

fraction are not changed.

The Rl and R2 fields must designate register0, 2,

4, or6; otherwise, a specification exception is recog

nized.

Resulting Condition Code:° Result fraction is zero

1 -

2 Result is greater than zero

3 -

Program Exceptions:

JOperation (if the floating-point feature is not

installed)

Specification

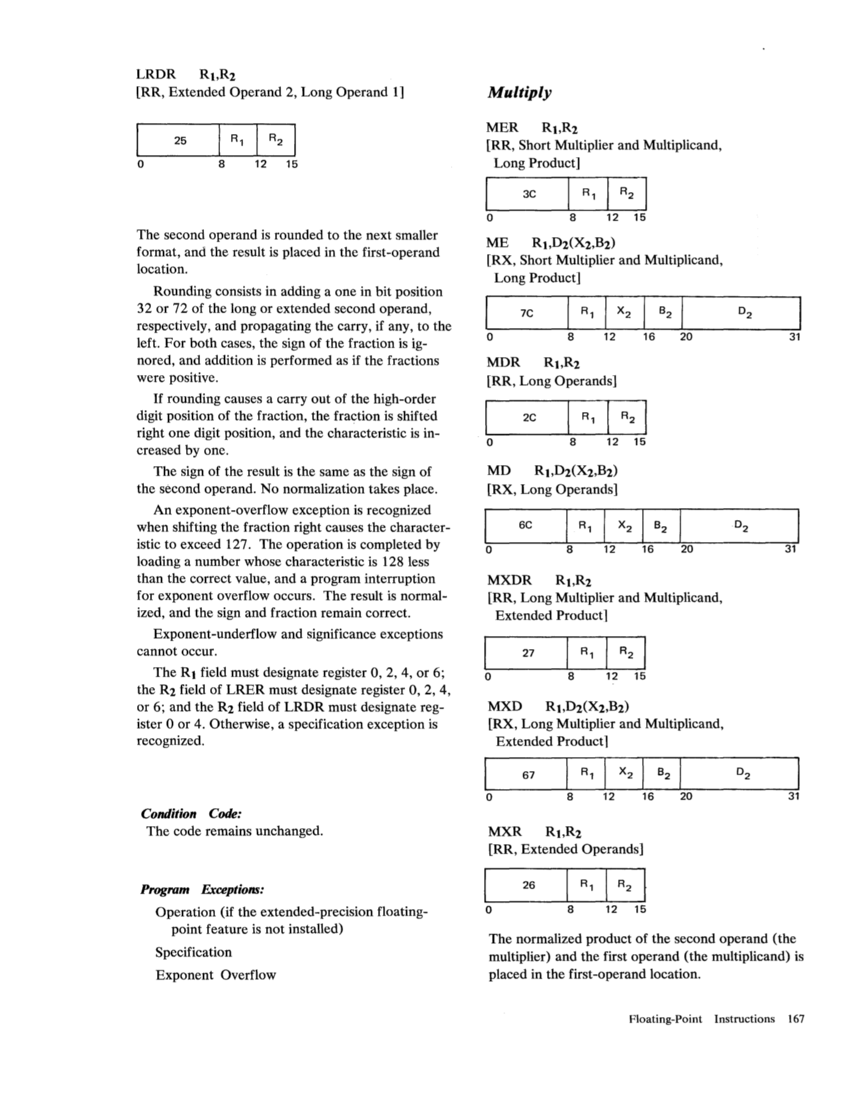

Load Rounded

LRER Rl,R2

[RR, LongOperand 2, Short Operand 1]

35

o 8 12 15

[RR, Long

location

The sign bit is inverted, even if the fraction is

zero. The

changed.

The Rl and R2 fields must designate register

4, or

nized.

Resulting Condition Code:

1 Result

2 Result

3 -

Program

installed)

Specification

Load Negative

LNER Rl,R2

[RR,

[RR, Long

The second operand is placed in the first-operand

location with the sign made minus.

The sign bit is made one, even if the fraction is

zero. The characteristic and fraction are not

changed.

The Rl and R2 fields must designate register

4, or

nized.

166

1 Result is less than zero

2 -

3 -

Program Exceptions:

installed)

Specification

Load Positive

[RR,

[RR, Long

The second operand is placed in the first-operand

location with the sign made plus.

The sign bit is made zero. The characteristic and

fraction are not changed.

The Rl and R2 fields must designate register

4, or

nized.

Resulting Condition Code:

1 -

2 Result is greater than zero

3 -

Program Exceptions:

J

installed)

Specification

Load Rounded

LRER Rl,R2

[RR, Long

35

o 8 12 15