stored is the address that is used to reference: storage

after dynamic address translation and prefixing, if

any, have been applied.

Region Code: The word at location 252 contains

model-dependent information which more specifical

ly defines the location of the error. For example, it

may contain a model-dependent address of the unit

causingan external damage or recovery report.

Register Save Area:On all machine-check interrup

tions,the addressable registers are saved sequentially

in storage. Floating-point registers0, 2, 4, and 6 are

stored starting at location 352; when the floating

point feature is not installed, these locationsare left

unchanged. General registers0-15 are stored start

ing atlocation 384, and control registers 0-15 are

stored starting at location 448. The information

stored for control-register positions not associated

with an installed feature is unpredictable.

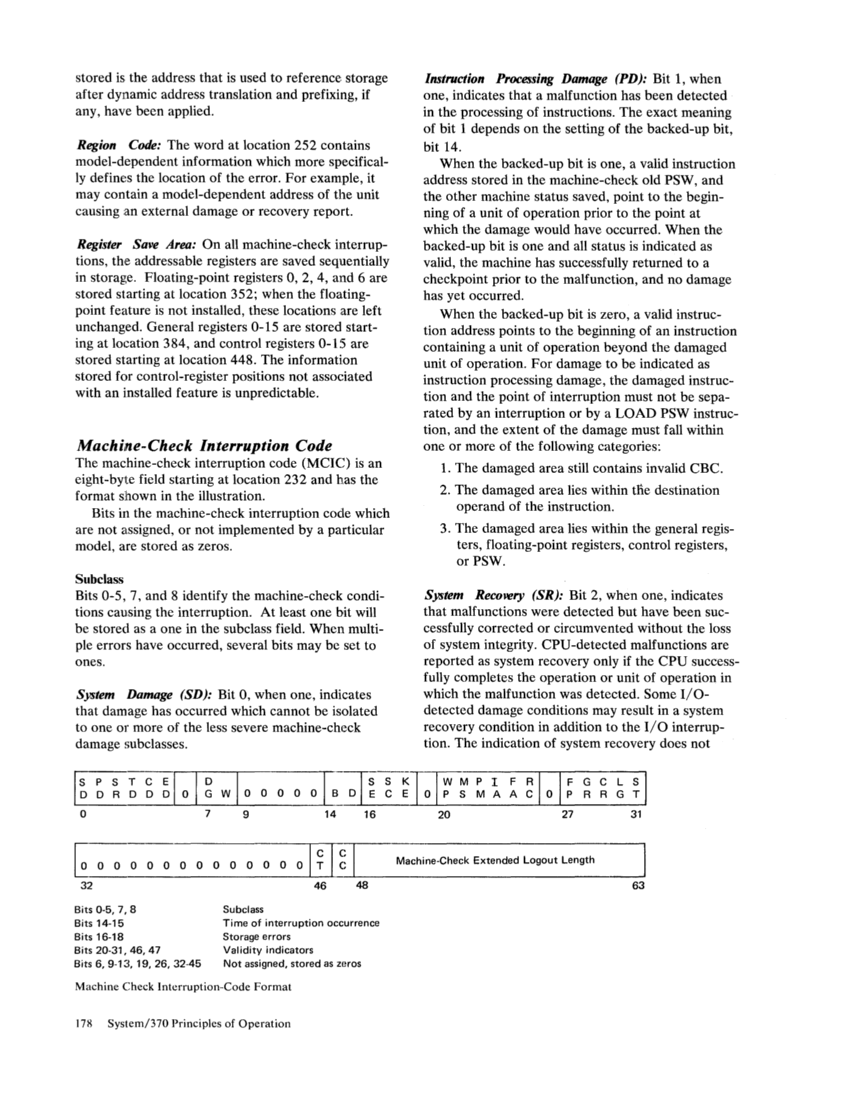

Machijne-Check Interruption Code

The machine-check interruption code (MCIC) is an

eight-byte field starting at location 232 and has the

format shown in the illustration.

Bits in the machine-check interruption code which

are notassigned, or not implemented by a particular

model, are stored as zeros.

Subclass

Bits0-5, 7, and 8 identify the machine-check condi

tions causing the interruption. At least one bit will

be stored as a one in the subclass field. When multi

ple errors have occurred, several bits may be set to

ones.

System Damage (SD): Bit0, when one, indicates

that damage has occurred which cannot be isolated

to one or more of the less severe machine-check

damage subclasses.

Instruction Processing Damage (PD): Bit 1, when

one, indicates that a malfunction has been detected

in the processing of instructions. The exact meaning

of bit 1 depends on the setting of the backed-up bit,

bit 14.

When the backed-up bit is one, a valid instruction

address stored in the machine-check oldPSW, and

the other machine status saved, point to the begin

ning of a unit of operation prior to the point at

which the damage would have occurred. When the

backed-up bit is one and all status is indicated as

valid, the machine has successfully returned to a

checkpoint prior to the malfunction, and no damage

has yet occurred.

When the backed-up bit is zero, a valid instruc

tion address points to the beginning of an instruction

containing a unit of operation beyond the damaged

unit of operation. For damage to be indicated as

instruction processing damage, the damaged instruc

tion and the point of interruption must not be sepa

rated by an interruption or by aLOAD PSW instruc

tion, and the extent of the damage must fall within

one or more of the following categories:

1. The damaged area still contains invalid CBC.

2. The damaged area lies withintIle destination

operand of the instruction.

3. The damaged area lies within the general regis

ters, floating-point registers, control registers,

orPSW. System Recovery (SR): Bit 2, when one, indicates

that malfunctions were detected but have been suc

cessfully corrected or circumvented without the loss

of system integrity. CPU-detected malfunctions are

reported as system recovery only if theCPU success

fully completes the operation or unit of operation in

which the malfunction was detected.Some 1/0- detected damage conditions may result in a system

recovery condition in addition to the110 interrup

tion. The indication of system recovery does notG 0 0 0 0 0 0 0 0 0 0 0 I I --' 0-5, 7, 8

Bits 14-15

Bits 16-18

Bits 20-31,46,47

Bits 6, 9-13,19,26,32-45Subclass Time of interruption occurrence Storage errors Validity indicators

Not assigned, stored as zeros

MachineCheck Interruption-Code Format

178 System/370Principles of Operation

63

after dynamic address translation and prefixing, if

any, have been applied.

Region Code: The word at location 252 contains

model-dependent information which more specifical

ly defines the location of the error. For example, it

may contain a model-dependent address of the unit

causing

Register Save Area:

tions,

in storage. Floating-point registers

stored starting at location 352; when the floating

point feature is not installed, these locations

unchanged. General registers

ing at

stored starting at location 448. The information

stored for control-register positions not associated

with an installed feature is unpredictable.

Machijne-Check Interruption Code

The machine-check interruption code (MCIC) is an

eight-byte field starting at location 232 and has the

format shown in the illustration.

Bits in the machine-check interruption code which

are not

model, are stored as zeros.

Subclass

Bits

tions causing the interruption. At least one bit will

be stored as a one in the subclass field. When multi

ple errors have occurred, several bits may be set to

ones.

System Damage (SD): Bit

that damage has occurred which cannot be isolated

to one or more of the less severe machine-check

damage subclasses.

Instruction Processing Damage (PD): Bit 1, when

one, indicates that a malfunction has been detected

in the processing of instructions. The exact meaning

of bit 1 depends on the setting of the backed-up bit,

bit 14.

When the backed-up bit is one, a valid instruction

address stored in the machine-check old

the other machine status saved, point to the begin

ning of a unit of operation prior to the point at

which the damage would have occurred. When the

backed-up bit is one and all status is indicated as

valid, the machine has successfully returned to a

checkpoint prior to the malfunction, and no damage

has yet occurred.

When the backed-up bit is zero, a valid instruc

tion address points to the beginning of an instruction

containing a unit of operation beyond the damaged

unit of operation. For damage to be indicated as

instruction processing damage, the damaged instruc

tion and the point of interruption must not be sepa

rated by an interruption or by a

tion, and the extent of the damage must fall within

one or more of the following categories:

1. The damaged area still contains invalid CBC.

2. The damaged area lies within

operand of the instruction.

3. The damaged area lies within the general regis

ters, floating-point registers, control registers,

or

that malfunctions were detected but have been suc

cessfully corrected or circumvented without the loss

of system integrity. CPU-detected malfunctions are

reported as system recovery only if the

fully completes the operation or unit of operation in

which the malfunction was detected.

recovery condition in addition to the

tion. The indication of system recovery does not

Bits 14-15

Bits 16-18

Bits 20-31,46,47

Bits 6, 9-13,19,26,32-45

Not assigned, stored as zeros

Machine

178 System/370

63