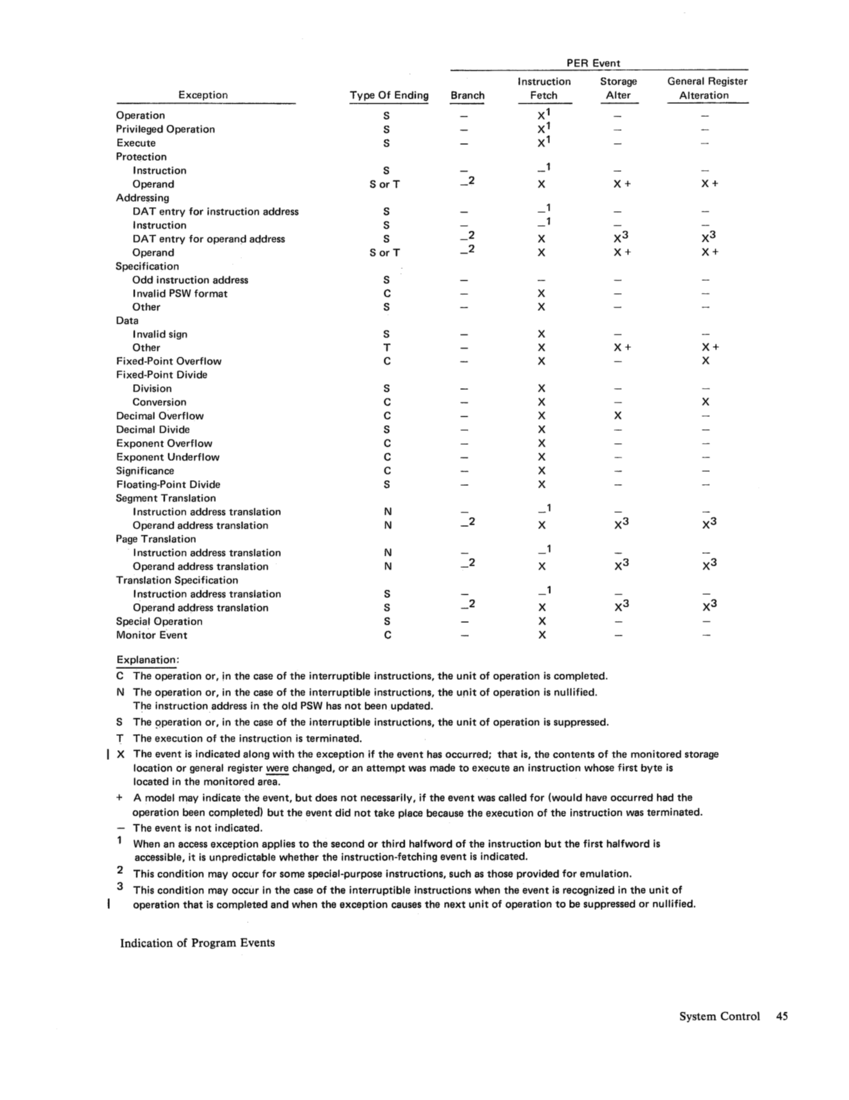

PER Event

Exception TypeOf Ending S Branch Instruction Fetch

StorageAlter Operation Privileged Operation

Execute

ProtectionInstruction Operand OAT entry for instruction address Instruction OAT entry for operand address Operand Specification Odd instruction address Invalid PSW format Other Data I nvalid sign Other Fixed-Point Overflow Fixed-Point Divide

Division

ConversionDecimal Overflow Decimal Divide

ExponentOverflow Exponent Underflow Significance

Floating-Point Divide

SegmentTranslation I nstruction address translation Operand address translation Page Translation I nstruction address translation Operand address translation Translation Specification I nstruction address translation Operand address translation Special Operation

Monitor EventExplanation: S S S SorT S S S SorT S C S S T

CS C

CS C

C

CS N

N

N

NS S S C

2

2

2

2

2

x

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1

1

1

X

X

1

X

X

X

C

The operation or,in the case of the interruptible instructions, the unit of operation is completed. N

The operation or, in the case of theinterruptible instructions, the unit of operation is nullified. The instruction address in the old PSW has not been updated. S The 9peration or, in the case of the interruptible instructions, the unit of operation is suppressed.

T The execution of the instrL!ction is terminated.

X+

X3

X+

X+

XGeneral Register Alteration X+

X3

X+

X+

X

X

X The event is indicatedalong with the exception if the event has occurred; that is, the contents of the monitored storage location or general register located in the monitored area.

+ Amodel may indicate the event, but does not necessarily, if the event was called for (would have occurred had the

operation beencompleted) but the event did not take place because the execution of the instruction was terminated.

The event is not indicated.

When an access exceptionapplies to the second or third halfword of the instruction but the first halfword is accessible, it is unpredictable whether the instruction-fetching event is indicated.

2 This condition may occur for somespecial-purpose instructions, such as those provided for emulation. 3 This condition may occur in the case of the interruptible instructions when the event is recognized in the unit of

operation that iscompleted and when the exception causes the next unit of operation to be suppressed or nullified. Indication of Program Events

System Control 45

Exception Type

Storage

Execute

Protection

Division

Conversion

Exponent

Floating-Point Divide

Segment

Monitor Event

C

C

C

C

N

N

N

2

2

2

2

2

x

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

1

1

1

X

X

1

X

X

X

C

The operation or,

The operation or, in the case of the

T The execution of the instrL!ction is terminated.

X+

X3

X+

X+

X

X3

X+

X+

X

X

X The event is indicated

+ A

operation been

The event is not indicated.

When an access exception

2 This condition may occur for some

operation that is

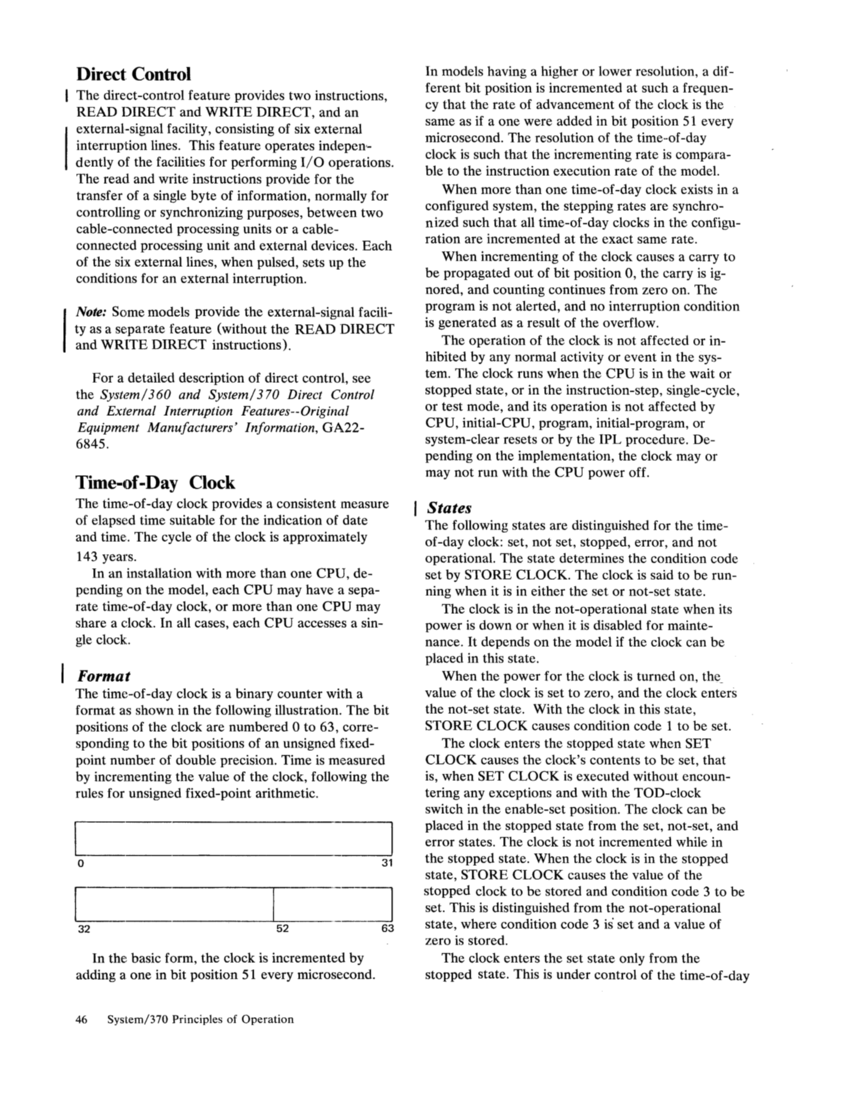

System Control 45