yoked. With a 4,096-byte page size, two keys are

associated with a page.

Programming Note

Theaccuracy of reference recording is such as to

allow for effective operation of paging algorithms.

The: reference bit cannot be used to establish the

usage of pages containing translation tables since,

after the initial reference, the tables may be used by

means of references to the translation-Iookaside

buffer, without any fetching of the table entries from

main storage.Address- Translation Exceptions

When the dynamic-address-translation facility isinstallc!d, three additional program-exception condi

tions(llre introduced: segment-translation exception, page-translation exception, and translation

specification exception. TheCPU cannot be disabled

forTht! presence .of the dynamic-address-translation

facility also introduces new conditions that are recognized as addressing exceptions. When address

translation is invoked, an addressing exception is

recognized when an attempt is made to use a

segment-table entry or a page-table entry that is

designated at a location outside the available main

storage of the installed system. The unitof operation

is suppressed.

The handling of all exceptions associated with

dynamic address translation is summarized in the

table "Handling of Access Exceptions" in the chap

ter"Interruptions." Summary of Dynamic Address

Translation Formats

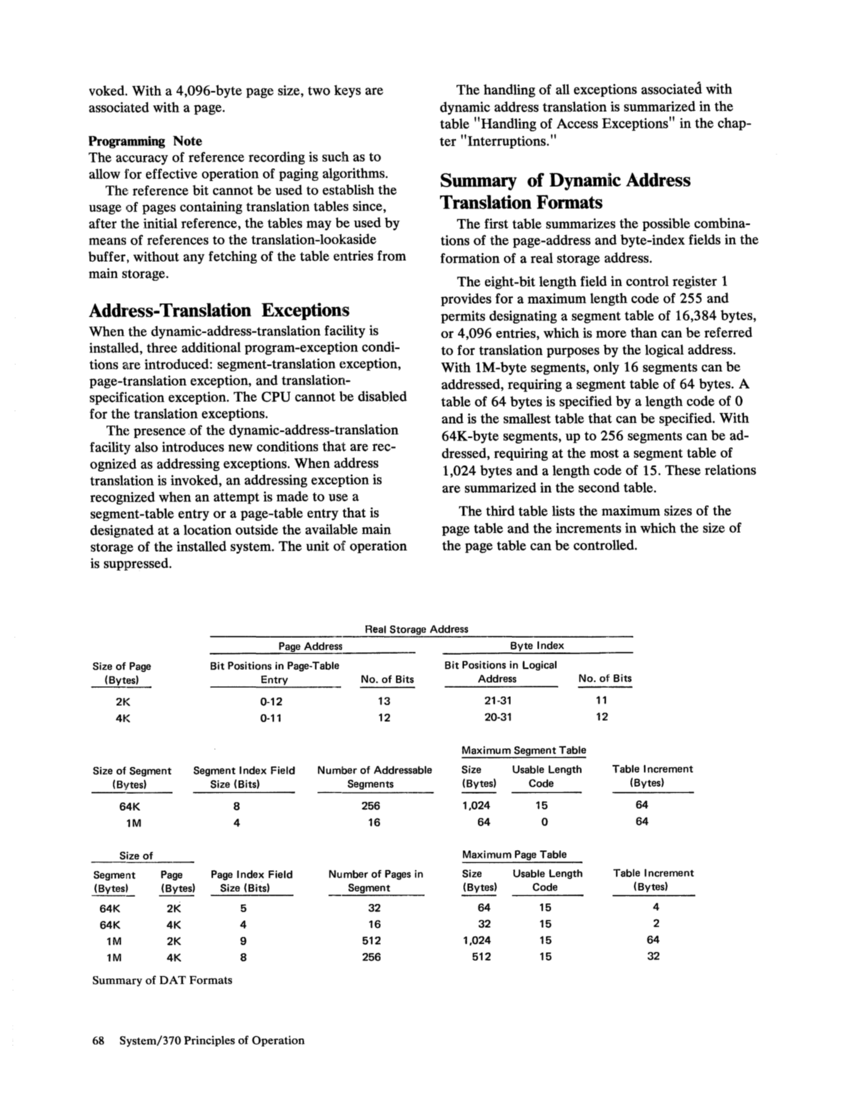

The first table summarizes the possible combina

tions of the page-address and byte-index fields in the

formation of a real storage address.

The eight-bit length field in control register 1

provides for a maximum length code of 255 and

permits designating a segment table of 16,384 bytes,

or 4,096 entries, which is more than can be referred

to for translation purposes by the logical address.

With 1M-byte segments, only 16 segments can be

addressed, requiring a segment table of 64 bytes. A

table of 64 bytes is specified by a length code of° and is the smallest table that can be specified. With

64K-byte segments, up to 256 segments can be ad

dressed, requiring at the most a segment table of

1,024 bytes and a length code of 15. These relations

are summarized in the second table.

The third table lists the maximum sizes of the

page table and the increments in which the size of

the page table can be controlled.Real Storage Address

Page AddressSize of Page Bit Positions in Page-Table 2K 4K Size of Segment

(Bvtes)

64K

1MSize of

Segment Page

Entry0-12 0-11 Segment I ndex Field Size (Bits)

8

4

PageI ndex Field Size (Bits)

64K 2K 5

64K 4K 4

1M 2K 9

1M 4K 8

Summary of DAT Formats

68System/370 Principles of Operation No. of Bits

13

12

Number of Addressable

Segments

256

16

Number of Pages in

Segment

32

16

512

256

ByteIndex Bit Positions in Logical Address No. of Bits

21-3120-31 Maximum Segment Table Size Usable Length

(Bytes) Code1,024 15

640 Maximum Page Table Size Usable Length

(Bytes) Code

64 15

32 151,024 15

512 15

11

12Table Increment (Bytes)

64

64Table Increment (Bytes)

4

2

64

32

associated with a page.

Programming Note

The

allow for effective operation of paging algorithms.

The: reference bit cannot be used to establish the

usage of pages containing translation tables since,

after the initial reference, the tables may be used by

means of references to the translation-Iookaside

buffer, without any fetching of the table entries from

main storage.

When the dynamic-address-translation facility is

tions

specification exception. The

for

facility also introduces new conditions that are rec

translation is invoked, an addressing exception is

recognized when an attempt is made to use a

segment-table entry or a page-table entry that is

designated at a location outside the available main

storage of the installed system. The unit

is suppressed.

The handling of all exceptions associated with

dynamic address translation is summarized in the

table "Handling of Access Exceptions" in the chap

ter

Translation Formats

The first table summarizes the possible combina

tions of the page-address and byte-index fields in the

formation of a real storage address.

The eight-bit length field in control register 1

provides for a maximum length code of 255 and

permits designating a segment table of 16,384 bytes,

or 4,096 entries, which is more than can be referred

to for translation purposes by the logical address.

With 1M-byte segments, only 16 segments can be

addressed, requiring a segment table of 64 bytes. A

table of 64 bytes is specified by a length code of

64K-byte segments, up to 256 segments can be ad

dressed, requiring at the most a segment table of

1,024 bytes and a length code of 15. These relations

are summarized in the second table.

The third table lists the maximum sizes of the

page table and the increments in which the size of

the page table can be controlled.

Page Address

(Bvtes)

64K

1M

Segment Page

Entry

8

4

Page

64K 2K 5

64K 4K 4

1M 2K 9

1M 4K 8

Summary of DAT Formats

68

13

12

Number of Addressable

Segments

256

16

Number of Pages in

Segment

32

16

512

256

Byte

21-31

(Bytes) Code

64

(Bytes) Code

64 15

32 15

512 15

11

12

64

64

4

2

64

32