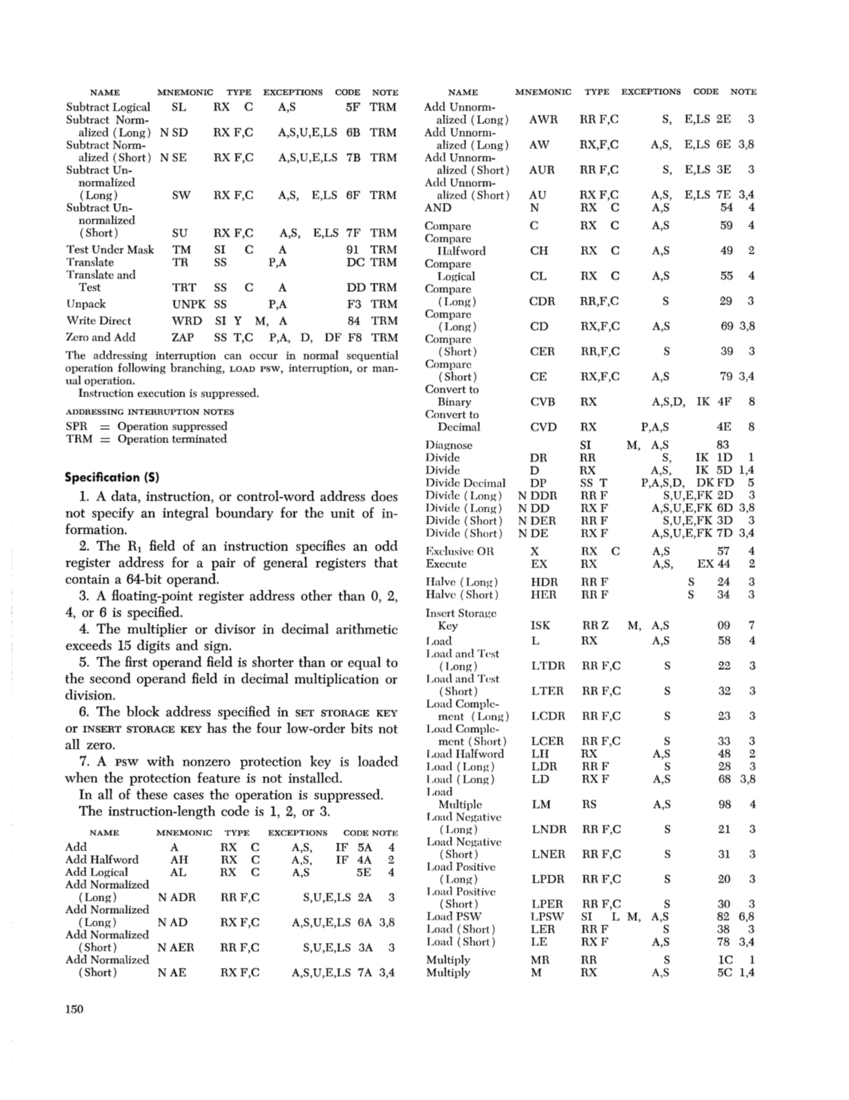

NAME MNEMONIC TYPE Subtract Logical SL RX C

Subtract Norm-

alized (Long) NSD RX F,C

Subtract Norm-

alized (Short) NSE RX F,C

SubtractUn- normalized

(Long)

SubtractUn normalized

( Short)

TestUnder Mask

Translate

Translate and

TestSW RX F,C SU RX F,C

TMSI C

TRSS TRT SS C UNPK SS EXCEPTIONS CODE NOTE A,S 5F TRM A,S,U,E,LS 6B TRM A,S,U,E,LS 7B TRM

A,S, E,LS 6F TRM

A,S, E,LS 7F TRM

A 91 TRMP,A DC TRM

A DDTRMP,A F3 TRM Unpack Write Direct

Zero and Add'VRD SI Y M, A 84 TRM ZAP SS T,C P,A, D, DF F8 TRM

The addressing interruption can occur in normal sequential

operation following branching,LOAD PSW, interruption, or man

ual operation.

Instruction execution is suppressed.

ADDRESSINGINTERRUPTION NOTES SPR Operation suppressed

TRM = Operation terminatedSpecification (S) 1. A data, instruction, or control-word address does

not specify an integral boundary for the unit of in

formation.

2. The Rl field of an instruction specifies an odd

register address for a pair of general registers that

contain a 64-bit operand.

3. A floating-point register address other than0, 2,

4, or 6 is specified.

4. The multiplier or divisor in decimal arithmetic

exceeds 15 digits and sign.

5. The first operand field is shorter than or equal to

the second operand field in decimal multiplication or

division.

6. The block address specified inSET STORAGE KEY

orINSERT STORAGE KEY has the four low-order bits not

all zero.

7. A psw with nonzero protection key is loaded

when the protection feature is not installed.

In all of these cases the operation is suppressed.

The instruction-length code is 1, 2, or 3.

NAMEMNEMONIC Add A

Add Halfword AH

Add Logical AL

Add Normalized

(Long) N ADR

Add Normalized

(Long) N AD

Add Normalized

( Short) N AER

Add NormaHzed

(Short) N AE150 TYPE RX C

RX C

RX C

RRF,C

RXF,C

RRF,C

RXF,CEXCEPTIONS A,S,

A,S,A,S CODE NOTE IF 5A 4

IF 4A 2

5E 4S,U,E,LS 2A 3 A,S,U,E,LS 6A 3,8 S,U,E,LS 3A 3 A,S,U,E,LS 7A 3,4

NAME

AddUnnorm alized (Long)

AddUnnorm alizcd (Long)

AddUn norm

alized (Short)

AddUnnorm alized (Short)

AND

Compare

Compare

I Ialfword

Compare

Logical

Compare

(Long)

Compare

(Long)

Compare

(Short) Compare

( Short)

Convert to

Binary

Convert to

Decimal

Diagnose

Divide

Divide

Divide Dccimal

Dividc (Long)

Divide (Long)

Divide (Short)

Divide(Short) Exclusive OB Execute

Halve (Long)

Halve (Short)

InsertStorage Key

Load

Loadand Test (Long) I,oad and (Short) Load Comple

ment (Long)

Load Comple-

ment (Short)

Load Halfword

Load (Long)I,oad (Long) r,oad Multiple Load Negative

( Long)

Load Negative

(Short)

LoadPositive (Long)

T,oad Positive

(Short)

LoadPSW Load (Short) Load (Short)

Multiply

MultiplyMNEMONIC AWR

AWAUR AU N

C

CH

CL

CDR

CD

CER

CE

CVB

CVD

DR

DDP NDDR

NDD

NDER

NDE

X

EX

HDR

HERISK L

LTDR

LTER

LCDR

LCER

LH

LDR

LD

LM

LNDR

LNERLPDR LPER LPS\V LER

LE

MR

MTYPE EXCEPTIONS CODE NOTE

RRF,C

RX,F,C

RRF,C

RXF,C

RX C

RX C

RX C

RX C

RR,F,C

RX,F,C

RR,F,C

RX,F,CS, E,LS 2E 3

A,S, E,LS 6E 3,8S, E,LS 3E 3

A,S, E,LS 7E 3,4A,S 54 4 A,S A,S A,S S A,S S A,S 59 4

49 2

55 4

29 3

69 3,8

39 3

79 3,4

RX A,S,D, IK 4F 8

RXSI RR

RXSS T

RRF

RXF

RRF

RXF

RX C

RX

RRF

RRFP,A,S 4E 8

M,A,S 83 S, IK ID 1

A,S, IK 5D 1,4P,A,S,D, DK FD 5 S,U,E,FK 2D 3

A,S,U ,E,FK 6D 3,8 S,U,E,FK 3D 3 A,S,U,E,FK 7D 3,4 A,S 57 4

A,S, EX 44 2S 24 3 S 34 3

RRZ M,A,S 09 7

RXA,S RR F,C S RR F,C S RR F,C S RRF,C

RX

RRF

RXFRS RRF,C

RRF,C

RRF,CS A,S S A,S A,S S S S RR F,C S SI L M, A,S RRF S RX FA,S

RR

RXS A,S 58 4

22 3

32 3

23 3

33 3

48 2

28 3

68 3,8

98 4

21 3

31 320 3 30 3

82 6,8

38 3

78 3,4

lC 1

5C 1,4

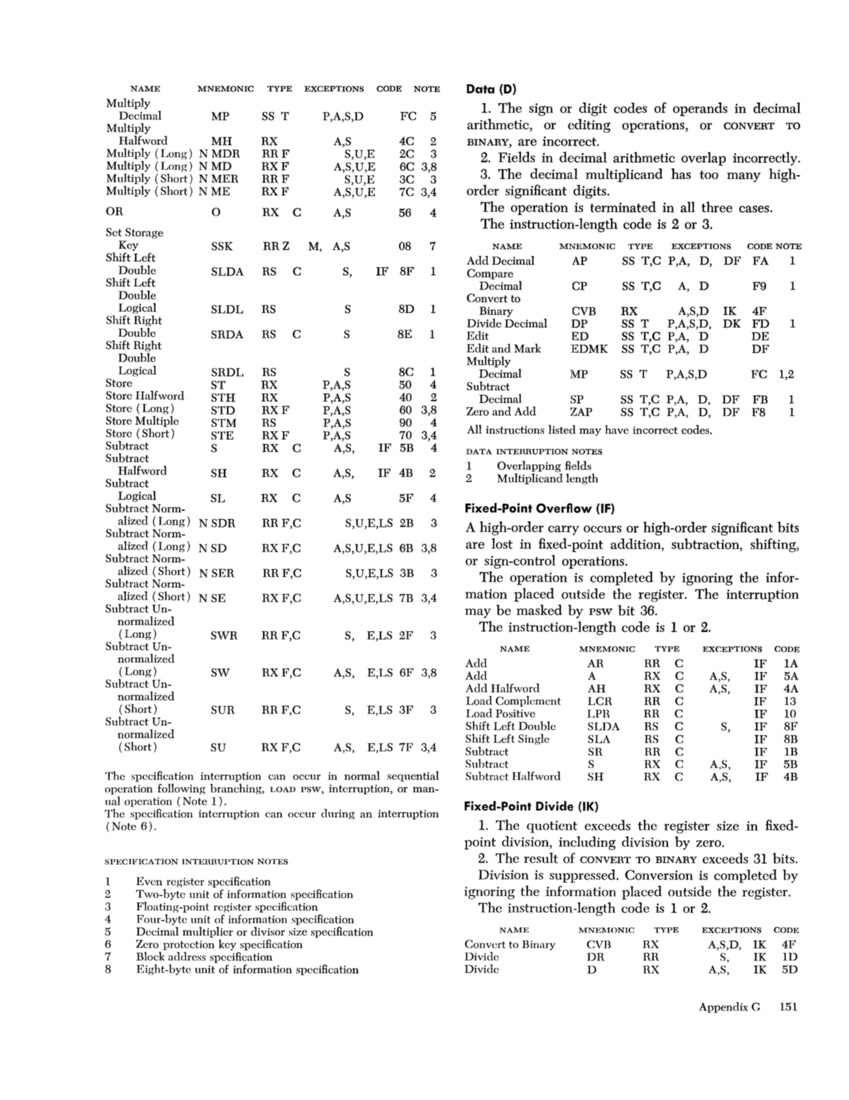

Subtract Norm-

alized (Long) N

Subtract Norm-

alized (Short) N

Subtract

(Long)

Subtract

( Short)

Test

Translate

Translate and

Test

TM

TR

A,S, E,LS 6F TRM

A,S, E,LS 7F TRM

A 91 TRM

A DDTRM

Zero and Add

The addressing interruption can occur in normal sequential

operation following branching,

ual operation.

Instruction execution is suppressed.

ADDRESSING

TRM = Operation terminated

not specify an integral boundary for the unit of in

formation.

2. The Rl field of an instruction specifies an odd

register address for a pair of general registers that

contain a 64-bit operand.

3. A floating-point register address other than

4, or 6 is specified.

4. The multiplier or divisor in decimal arithmetic

exceeds 15 digits and sign.

5. The first operand field is shorter than or equal to

the second operand field in decimal multiplication or

division.

6. The block address specified in

or

all zero.

7. A psw with nonzero protection key is loaded

when the protection feature is not installed.

In all of these cases the operation is suppressed.

The instruction-length code is 1, 2, or 3.

NAME

Add Halfword AH

Add Logical AL

Add Normalized

(Long) N ADR

Add Normalized

(Long) N AD

Add Normalized

( Short) N AER

Add NormaHzed

(Short) N AE

RX C

RX C

RRF,C

RXF,C

RRF,C

RXF,C

A,S,

IF 4A 2

5E 4

NAME

Add

Add

Add

alized (Short)

Add

AND

Compare

Compare

I Ialfword

Compare

Logical

Compare

(Long)

Compare

(Long)

Compare

(

( Short)

Convert to

Binary

Convert to

Decimal

Diagnose

Divide

Divide

Divide Dccimal

Dividc (Long)

Divide (Long)

Divide (Short)

Divide

Halve (Long)

Halve (Short)

Insert

Load

Load

ment (Long)

Load Comple-

ment (Short)

Load Halfword

Load (Long)

( Long)

Load Negative

(Short)

Load

T

(Short)

Load

Multiply

Multiply

AW

C

CH

CL

CDR

CD

CER

CE

CVB

CVD

DR

D

NDD

NDER

NDE

X

EX

HDR

HER

LTDR

LTER

LCDR

LCER

LH

LDR

LD

LM

LNDR

LNER

LE

MR

M

RRF,C

RX,F,C

RRF,C

RXF,C

RX C

RX C

RX C

RX C

RR,F,C

RX,F,C

RR,F,C

RX,F,C

A,S, E,LS 6E 3,8

A,S, E,LS 7E 3,4

49 2

55 4

29 3

69 3,8

39 3

79 3,4

RX A,S,D, IK 4F 8

RX

RX

RRF

RXF

RRF

RXF

RX C

RX

RRF

RRF

M,

A,S, IK 5D 1,4

A,S,

A,S, EX 44 2

RRZ M,

RX

RX

RRF

RXF

RRF,C

RRF,C

RR

RX

22 3

32 3

23 3

33 3

48 2

28 3

68 3,8

98 4

21 3

31 3

82 6,8

38 3

78 3,4

lC 1

5C 1,4