Program Interruptions:

Addressing (AL only)

Specification (AL only)

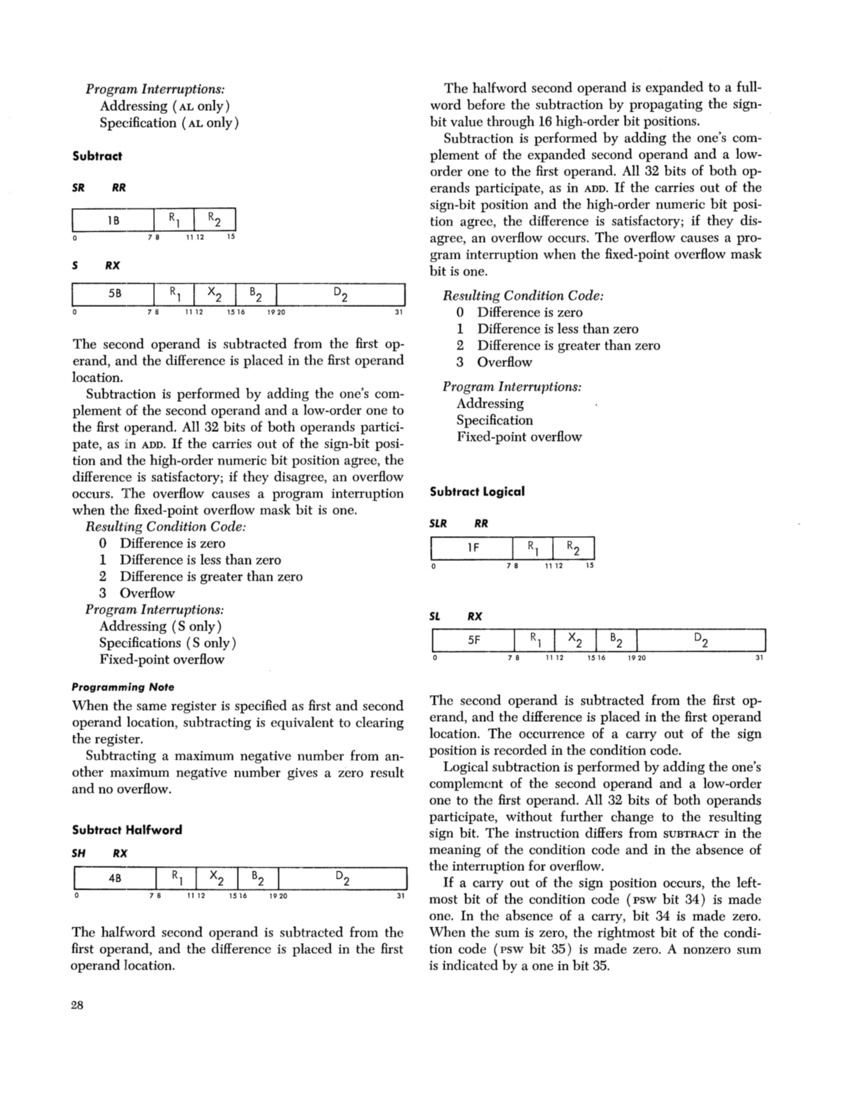

SubtractSR RR I 1B I R1 R2 0 78 11 12 15 S RX I 5B I R1

X

2

B2 D20 7 8 11 12 1516 1920 31

The second operand is subtracted from the first op

erand, and the difference is placed in the first operand

location.

Subtraction is performed by adding the one's com

plement.of the second operand and a low-order one to

the first operand. All 32 bits of both operands partici

pate, asin ADD. If the carries out of the sign-bit posi

tion and the high-order numeric bit position agree, the

difference is satisfactory; if they disagree, an overflow

occurs. The overflow causes a program interruption

when the fixed-point overflow mask bit is one.ResulUng Condition Code:

o Difference is zero

1 Difference is less than zero

2 Difference is greater than zero

3 OverflowProgram Interruptions:

Addressing(S only)

Specifications(S only)

Fixed-point overflow

Programming Note

When the same register is specified as first and second

operand location, subtracting is equivalent to clearing

the register.

Subtracting a maximum negative number from an

other maximum negative number gives a zero result

and no overflow.

Subtract:Halfword SH RX 4B

7 8 11 12 15 16 1 920 31

The halfword second operand is subtracted from the

first operand, and the difference is placed in the first

operand location.

28

The halfword second operand is expanded to a full

word before the subtraction by propagating the sign

bit value through 16 high-order bit positions.

Subtraction is performed by adding the one's com

plement of the expanded second operand and a low

order one to the first operand. All 32 bits of both op

erands participate, as in ADD. If the carries out of the

sign-bit position and the high-order numeric bit posi

tion agree, the difference is satisfactory; if they dis

agree, an overflow occurs. The overflow causes a pro

gram interruption when the fixed-point overflow mask

bit is one.

Resulting Condition Code:

o Difference is zero

1 Difference is less than zero

2 Difference is greater than zero

3Overflow Program Interruptions:

AddressingS pecifica tion

Fixed-point overflow

SubtractLogical SLR RR

1 F

78 1112 15SL RX

5F

7 8 11 1 2 15 16 1 920 31

The second operand is subtracted from the first op

erand, and the difference is placed in the first operand

location. The occurrence of a carry out of the sign

position is recorded in the condition code.

Logical subtraction is performed by adding the one's

complement of the second operand and a low-order

one to the first operand. All 32 bits of both operands

participate, without further change to the resulting

sign bit. The instruction differs fromSUBTRACT in the

meaning of the condition code and in the absence of

the interruption for overflow.

If a carry out of the sign position occurs, the left

most bit of the condition code (psw bit 34) is made

one. In the absence of a carry, bit 34 is made zero.

When the sum is zero, the rightmost bit of the condi

tion code (psw bit 35) is made zero. A nonzero sum

is indicated by a one in bit 35.

Addressing (AL only)

Specification (AL only)

Subtract

X

2

B2 D2

The second operand is subtracted from the first op

erand, and the difference is placed in the first operand

location.

Subtraction is performed by adding the one's com

plement

the first operand. All 32 bits of both operands partici

pate, as

tion and the high-order numeric bit position agree, the

difference is satisfactory; if they disagree, an overflow

occurs. The overflow causes a program interruption

when the fixed-point overflow mask bit is one.

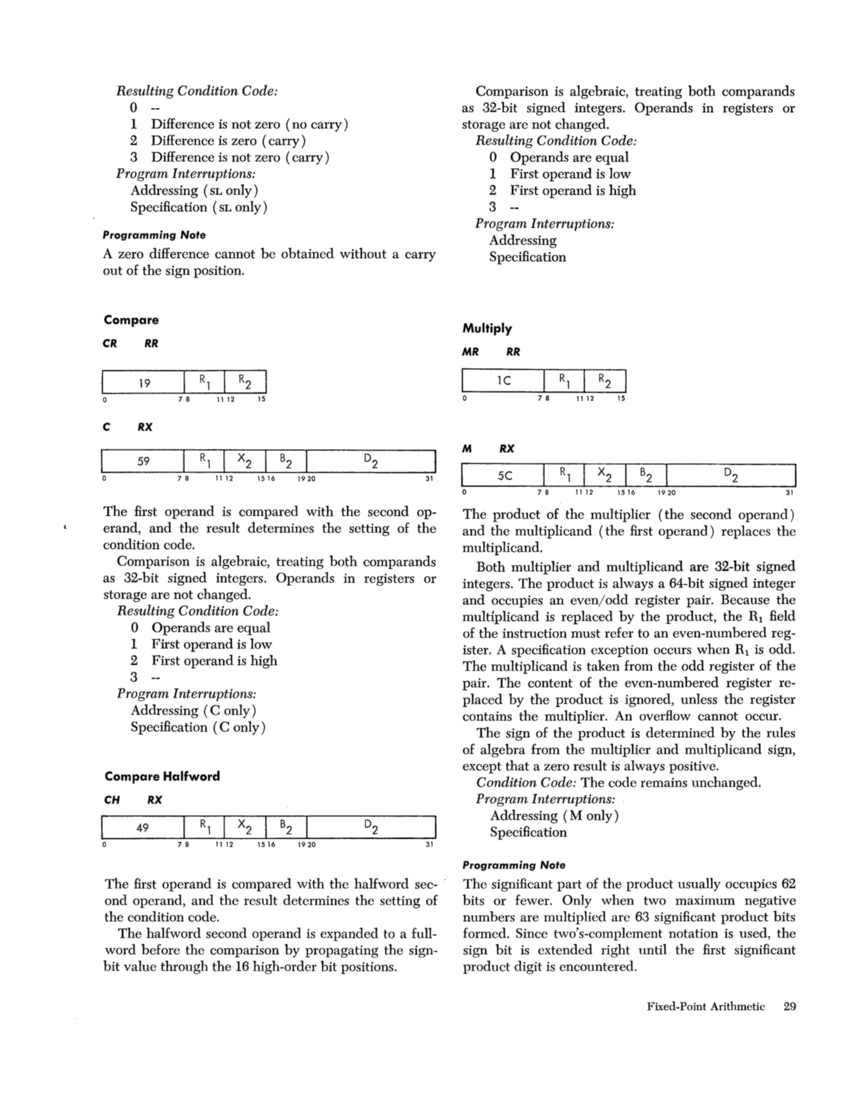

o Difference is zero

1 Difference is less than zero

2 Difference is greater than zero

3 Overflow

Addressing

Specifications

Fixed-point overflow

Programming Note

When the same register is specified as first and second

operand location, subtracting is equivalent to clearing

the register.

Subtracting a maximum negative number from an

other maximum negative number gives a zero result

and no overflow.

Subtract

7 8 11 12 15 16 1 9

The halfword second operand is subtracted from the

first operand, and the difference is placed in the first

operand location.

28

The halfword second operand is expanded to a full

word before the subtraction by propagating the sign

bit value through 16 high-order bit positions.

Subtraction is performed by adding the one's com

plement of the expanded second operand and a low

order one to the first operand. All 32 bits of both op

erands participate, as in ADD. If the carries out of the

sign-bit position and the high-order numeric bit posi

tion agree, the difference is satisfactory; if they dis

agree, an overflow occurs. The overflow causes a pro

gram interruption when the fixed-point overflow mask

bit is one.

Resulting Condition Code:

o Difference is zero

1 Difference is less than zero

2 Difference is greater than zero

3

Addressing

Fixed-point overflow

Subtract

1 F

78 1112 15

5F

7 8 11 1 2 15 16 1 9

The second operand is subtracted from the first op

erand, and the difference is placed in the first operand

location. The occurrence of a carry out of the sign

position is recorded in the condition code.

Logical subtraction is performed by adding the one's

complement of the second operand and a low-order

one to the first operand. All 32 bits of both operands

participate, without further change to the resulting

sign bit. The instruction differs from

meaning of the condition code and in the absence of

the interruption for overflow.

If a carry out of the sign position occurs, the left

most bit of the condition code (psw bit 34) is made

one. In the absence of a carry, bit 34 is made zero.

When the sum is zero, the rightmost bit of the condi

tion code (psw bit 35) is made zero. A nonzero sum

is indicated by a one in bit 35.