codes is interpreted as sign codes, with 1010, 1100, 1110, and 1111 recognized as plus and with 1011 and 1101 recognized as minus. The codes 0000-1001 are

invalid as sign codes. The zones are not tested for

valid codes as they are eliminated in changing data

from the zoned to the packed format.

The sign and zone codes generated for all decimal

arithmetic results differ for the extended binary-coded

decimal interchange code (EBCDIC) and the American

Standard code for information interchange (ASCII) .

The choice between the two codes is determined by

bit 12 of the psw. When bit 12 is zero, the preferred

EBCDIC codes are generated; these are plus,1100; minus, 1101; and zone, 1111. When bit 12 is one, the

preferredASCII codes are generated; these are plus, 1010; minus, 1011; and zone, 0101. Condition Code

The results of all add-type and comparison operations

are used to set the condition code. All other decimal

arithmetic operations leave the code unchanged. The

condition code can be used for deciSion-making by

subsequent branch-on-condition instructions.

The condition code can be set to reflect two types

of results for decimal arithmetic. For most operations

the states0, 1, and 2 indicate a zero, less than zero,

and greater than zero content of the result field; the

state 3 is used when the result of the operations over

flows.

For the comparison operation, the states0, 1, and 2

indicate that the first operand compared equal, low,

or high.

CONDITION CODESETTING FOR DECIMAL ARITHMETIC 0 1 2 3

Add Decimal zero < zero > zero overflowCompare Decimal equal low high

Subtract Decimal zero < zero > zero overflow

Zero and Add zero < zero > zero overflow

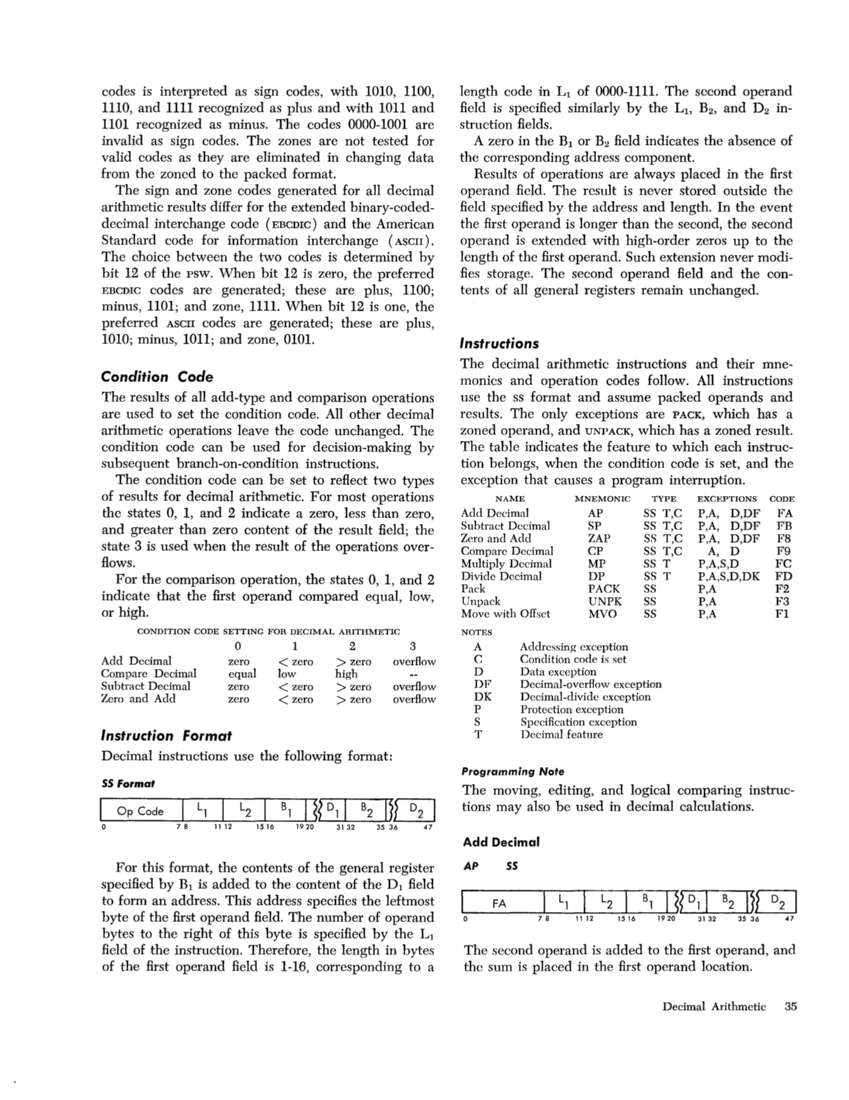

Instruction Format

Decimal instructions use the following format:55 Format Op Code B1 I I B2

For this format, the contents of the general register

specified by Bl is added to the content of the Dl field

to form an address. This address specifies the leftmost

byte of the first operand field. The number of operand

bytes to the right of this byte is specified by the Ll

field of the instruction. Therefore, the length in bytes

of the first operand field is 1-16, corresponding to a

length code in Ll of0000-1111. The second operand

field is specified similarly by the L1, B2, and D2 in

struction fields.

A zero in the Bl or B2 field indicates the absence of

the corresponding address component.

Results of operations are always placed in the first

operand field. The result is never stored outside the

field specified by the address and length. In the event

the first operand is longer than the second, the second

operand is extended with high-order zeros up to the

length of the first operand. Such extension never modi

fies storage. The second operand field and the con

tents of all general registers remain unchanged.

Instructions

The decimal arithmetic instructions and their mne

monics and operation codes follow. All instructions

use the ss format and assume packed operands and

results. The only exceptions arePACK, which has a

zoned operand, andUNPACK, which has a zoned result.

The table indicates the feature to which each instruc

tion belongs, when the condition code is set, and the

exception that causes a program interruption.

NAME MNEMONIC

Add DecimalAP Subtract Decimal SP Zero and Add ZAP Compare Decimal CP Multiply Decimal MP Divide Decimal DP Pack PACK Unpack UNPK Move with Offset MVO NOTES Addressing exception Condition code is set

TYPESS T,C SS T,C SS T,C SS T,C SS T SS T SS SS SS A C D

DF

DKP S T

Data exception

Decimal-overflow exception

Decimal-divide exception

Protection exception

Specification exception

Decimal feature

Programming Note

EXCEPTIONS CODEP,A, D,DF FA P,A, D,DF FB P,A, D,DF F8

A, D F9P,A,S,D FC P,A,S,D,DK FD P,A F2 P,A F3 P,A Fl

The moving, editing, and logical comparing instruc

tions may also be used in decimal calculations.

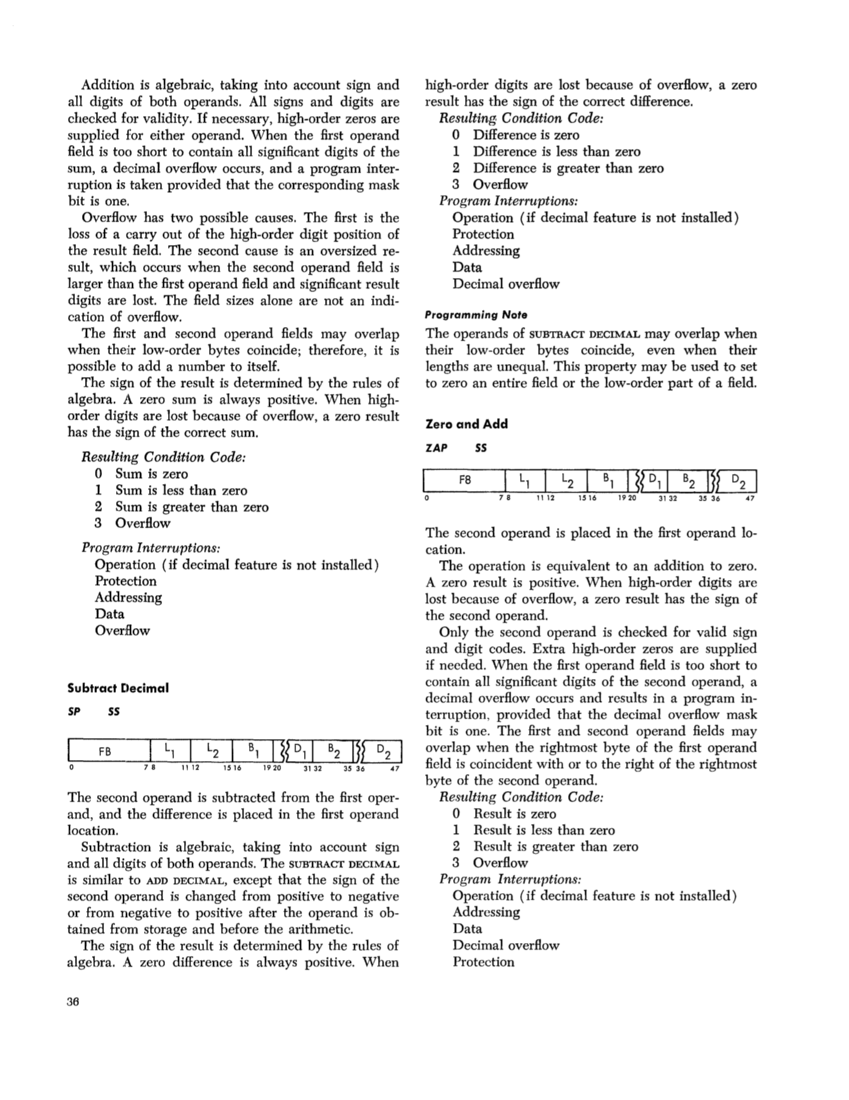

AddDecimal AP 55 FA B1 I 1 B2 IJ[5] 7 8 11 12 1516 1920 31 32 35 36 47

The second operand is added to the first operand, and

the sum is placed in the first operand location.

Decimal Arithmetic 35

invalid as sign codes. The zones are not tested for

valid codes as they are eliminated in changing data

from the zoned to the packed format.

The sign and zone codes generated for all decimal

arithmetic results differ for the extended binary-coded

decimal interchange code (EBCDIC) and the American

Standard code for information interchange (

The choice between the two codes is determined by

bit 12 of the psw. When bit 12 is zero, the preferred

EBCDIC codes are generated; these are plus,

preferred

The results of all add-type and comparison operations

are used to set the condition code. All other decimal

arithmetic operations leave the code unchanged. The

condition code can be used for deciSion-making by

subsequent branch-on-condition instructions.

The condition code can be set to reflect two types

of results for decimal arithmetic. For most operations

the states

and greater than zero content of the result field; the

state 3 is used when the result of the operations over

flows.

For the comparison operation, the states

indicate that the first operand compared equal, low,

or high.

CONDITION CODE

Add Decimal zero < zero > zero overflow

Subtract Decimal zero < zero > zero overflow

Zero and Add zero < zero > zero overflow

Instruction Format

Decimal instructions use the following format:

For this format, the contents of the general register

specified by Bl is added to the content of the Dl field

to form an address. This address specifies the leftmost

byte of the first operand field. The number of operand

bytes to the right of this byte is specified by the Ll

field of the instruction. Therefore, the length in bytes

of the first operand field is 1-16, corresponding to a

length code in Ll of

field is specified similarly by the L1, B2, and D2 in

struction fields.

A zero in the Bl or B2 field indicates the absence of

the corresponding address component.

Results of operations are always placed in the first

operand field. The result is never stored outside the

field specified by the address and length. In the event

the first operand is longer than the second, the second

operand is extended with high-order zeros up to the

length of the first operand. Such extension never modi

fies storage. The second operand field and the con

tents of all general registers remain unchanged.

Instructions

The decimal arithmetic instructions and their mne

monics and operation codes follow. All instructions

use the ss format and assume packed operands and

results. The only exceptions are

zoned operand, and

The table indicates the feature to which each instruc

tion belongs, when the condition code is set, and the

exception that causes a program interruption.

NAME MNEMONIC

Add Decimal

TYPE

DF

DK

Data exception

Decimal-overflow exception

Decimal-divide exception

Protection exception

Specification exception

Decimal feature

Programming Note

EXCEPTIONS CODE

A, D F9

The moving, editing, and logical comparing instruc

tions may also be used in decimal calculations.

Add

The second operand is added to the first operand, and

the sum is placed in the first operand location.

Decimal Arithmetic 35