Specification Exception

A specification exception is recognized when:

1. A data, instruction, or control-word address does

not specify an integral boundary for the unit of in

formation.

2. The Rl field of an instruction specifies an odd

register address for a pair of general registers that

contains a 64-bit operand.

3. A floating-point register address other than0, 2,

4, or 6 is specified.

4. The multiplier or divisor in decimal arithmetic

exceeds 15 digits and sign.

5. The first operand field is shorter than or equal to

the second operand field in decimal multiplication or

division.

6. The block address specified in SETSTORAGE KEY or

INSERTSTORAGE KEY has the four low-order bits not

all zero.

7. A psw with nonzero protection key is loaded

and the protection feature is not installed.

The operation is suppressed. The instruction-length

code is 1, 2, or 3.

Data Exception

A data exception is recognized when:

1. The sign or digit codes of operands in decimal

arithmetic or editing operations or inCONVERT TO BINARY are incorrect.

2. Fields in decimal arithmetic overlap incorrectly.

3. The decimal multiplicand has too many high

order significant digits.

The operation is terminated. The instruction-length

code is 2 or 3.

Fixed-Point-Overflow Exception

When a high-order carry occurs or high-order signifi

cant bits are lost infixed-point add, subtract, shift, or

sign-control operations, a fixed-point-overflow excep

tion is recognized.

The operation is completed by ignoring the infor

mation placed outside the register. The interruption

may be masked by psw bit 36.

The instruction-length code is 1 or 2.

Fixed-Point-Divide Exception

A fixed-point-divide exception is recognized when a

quotient exceeds the register size infixed-pOint divi

sion, including division by zero, or the result ofCON VERT TO BINARY exceeds 31 bits.

Division is suppressed. Conversion is completed by

ignoring the information placed outside the register.

The instruction-length code is 1 or 2.Decimal-Overflow Exception

When the destination field is too small to contain the

result field in a decimal operation, a decimal-overflow

exception is recognized.

The operation is completed by ignoring the overflow

information. The interruption may be masked by psw

bit 37.

The instruction-length code is 3.

Decimal-Divide Exception

When a quotient exceeds the specified data field

size, a decimal-divide exception is recognized. The

operation is suppressed.

The instruction-length code is 3.

Exponent-Overflow Exception

When the result characteristic exceeds 127 in floating

point addition, subtraction, multiplication, or division,

an exponent-overflow exception is recognized. The

operation is terminated.

The instruction-length code is 1 or 2.Exponent-U nderflow Exception

When the result characteristic is less than zero in

floating-point addition, subtraction, multiplication, or

division, an exponent-underflow exception is rec

ognized.

The operation is completed by making the result a

true zero. The interruption may be masked by psw

bit 38.

The instruction-length code is 1 or 2.

Significance Exception

When the result of a floating-point addition or sub

traction has an all-zero fraction, a significance excep

tion is recognized.

The operation is completed. The interruption may

be masked by psw bit 39. The manner in which the

operation is completed is determined by the mask bit.

The instruction-length code is 1 or 2.

Floating-Point-Divide Exception

When division by a floating-point number with zero

fraction is attempted, a floating-point divide exception

is recognized. The operation is suppressed.

The instruction-length code is 1 or 2.

Supervisor-Col/Interruption

The supervisor-call interruption occurs as a result of

the execution ofSUPEHVISOR CALL.

The supervisor-call interruption causes the old psw

to be stored at location 32 and a new psw to be

fetched from location 96.

Interruptions 79

A specification exception is recognized when:

1. A data, instruction, or control-word address does

not specify an integral boundary for the unit of in

formation.

2. The Rl field of an instruction specifies an odd

register address for a pair of general registers that

contains a 64-bit operand.

3. A floating-point register address other than

4, or 6 is specified.

4. The multiplier or divisor in decimal arithmetic

exceeds 15 digits and sign.

5. The first operand field is shorter than or equal to

the second operand field in decimal multiplication or

division.

6. The block address specified in SET

INSERT

all zero.

7. A psw with nonzero protection key is loaded

and the protection feature is not installed.

The operation is suppressed. The instruction-length

code is 1, 2, or 3.

Data Exception

A data exception is recognized when:

1. The sign or digit codes of operands in decimal

arithmetic or editing operations or in

2. Fields in decimal arithmetic overlap incorrectly.

3. The decimal multiplicand has too many high

order significant digits.

The operation is terminated. The instruction-length

code is 2 or 3.

Fixed-Point-Overflow Exception

When a high-order carry occurs or high-order signifi

cant bits are lost in

sign-control operations, a fixed-point-overflow excep

tion is recognized.

The operation is completed by ignoring the infor

mation placed outside the register. The interruption

may be masked by psw bit 36.

The instruction-length code is 1 or 2.

Fixed-Point-Divide Exception

A fixed-point-divide exception is recognized when a

quotient exceeds the register size in

sion, including division by zero, or the result of

Division is suppressed. Conversion is completed by

ignoring the information placed outside the register.

The instruction-length code is 1 or 2.

When the destination field is too small to contain the

result field in a decimal operation, a decimal-overflow

exception is recognized.

The operation is completed by ignoring the overflow

information. The interruption may be masked by psw

bit 37.

The instruction-length code is 3.

Decimal-Divide Exception

When a quotient exceeds the specified data field

size, a decimal-divide exception is recognized. The

operation is suppressed.

The instruction-length code is 3.

Exponent-Overflow Exception

When the result characteristic exceeds 127 in floating

point addition, subtraction, multiplication, or division,

an exponent-overflow exception is recognized. The

operation is terminated.

The instruction-length code is 1 or 2.

When the result characteristic is less than zero in

floating-point addition, subtraction, multiplication, or

division, an exponent-underflow exception is rec

ognized.

The operation is completed by making the result a

true zero. The interruption may be masked by psw

bit 38.

The instruction-length code is 1 or 2.

Significance Exception

When the result of a floating-point addition or sub

traction has an all-zero fraction, a significance excep

tion is recognized.

The operation is completed. The interruption may

be masked by psw bit 39. The manner in which the

operation is completed is determined by the mask bit.

The instruction-length code is 1 or 2.

Floating-Point-Divide Exception

When division by a floating-point number with zero

fraction is attempted, a floating-point divide exception

is recognized. The operation is suppressed.

The instruction-length code is 1 or 2.

Supervisor-Col/Interruption

The supervisor-call interruption occurs as a result of

the execution of

The supervisor-call interruption causes the old psw

to be stored at location 32 and a new psw to be

fetched from location 96.

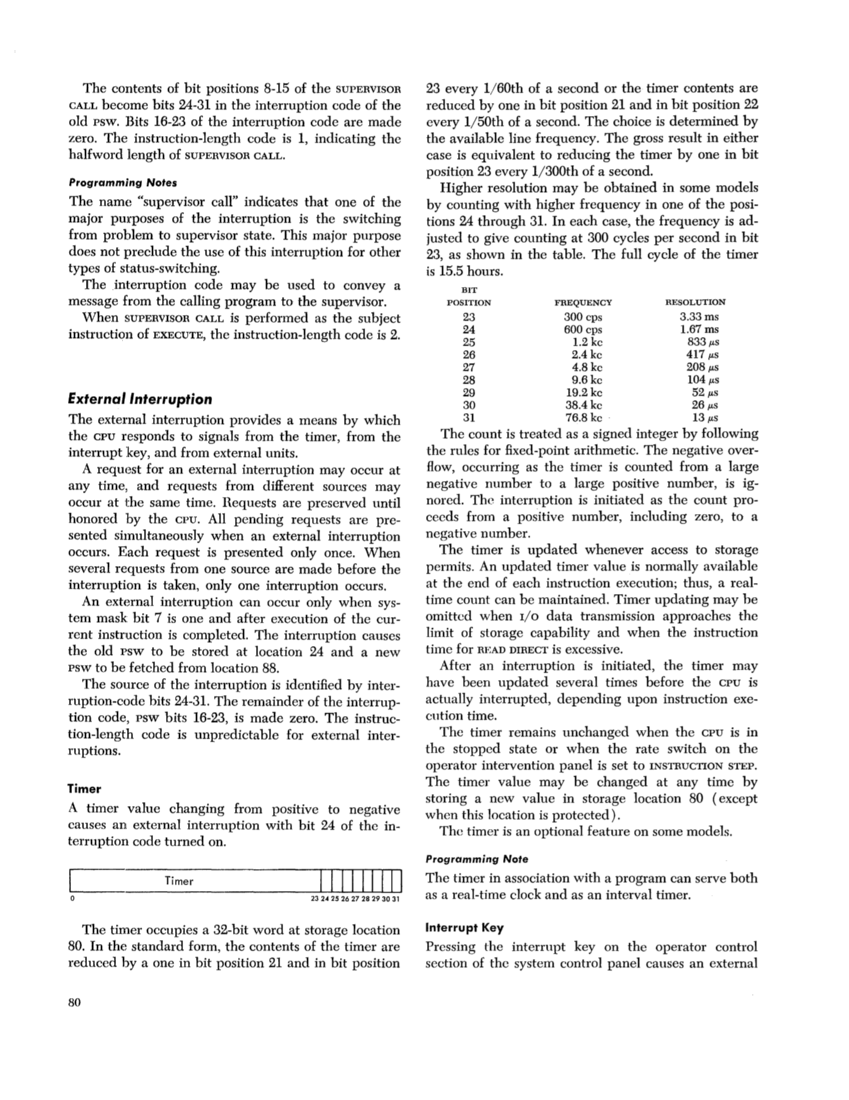

Interruptions 79