Control of Input/Output Devices

TheCPU controls I/O operations by means of four I/O instructions: START I/O, TEST I/O, HALT I/O, and TEST CHANNEL.

The instructionTEST CHANNEL addresscs a channel;

it does not address anI/O device. The other three I/O instructions address a channel and a device on that

channel.Input/Output Device Addressing

AnI/O device is designated by an I/O address. Each I/O address corresponds to a unique I/O device and is

specified by means of an II-bit binary number in theI/O instruction. The address identifies, for example, a

particular magnetic tape drive, disk access mcchanism,

or transmission line.

TheI/O address consists of two parts: channel ad

dress in the three high-order bit positions, and a device

address in theeight low-order bit positions. The chan

nel address specifies the channel to which the instruc

tion applies; the device address identifies the particularI/O device in that channel. Any number in the range 0-255 can be used as a device address, providing facili

ties for addressing 256 devices per channel. The assign

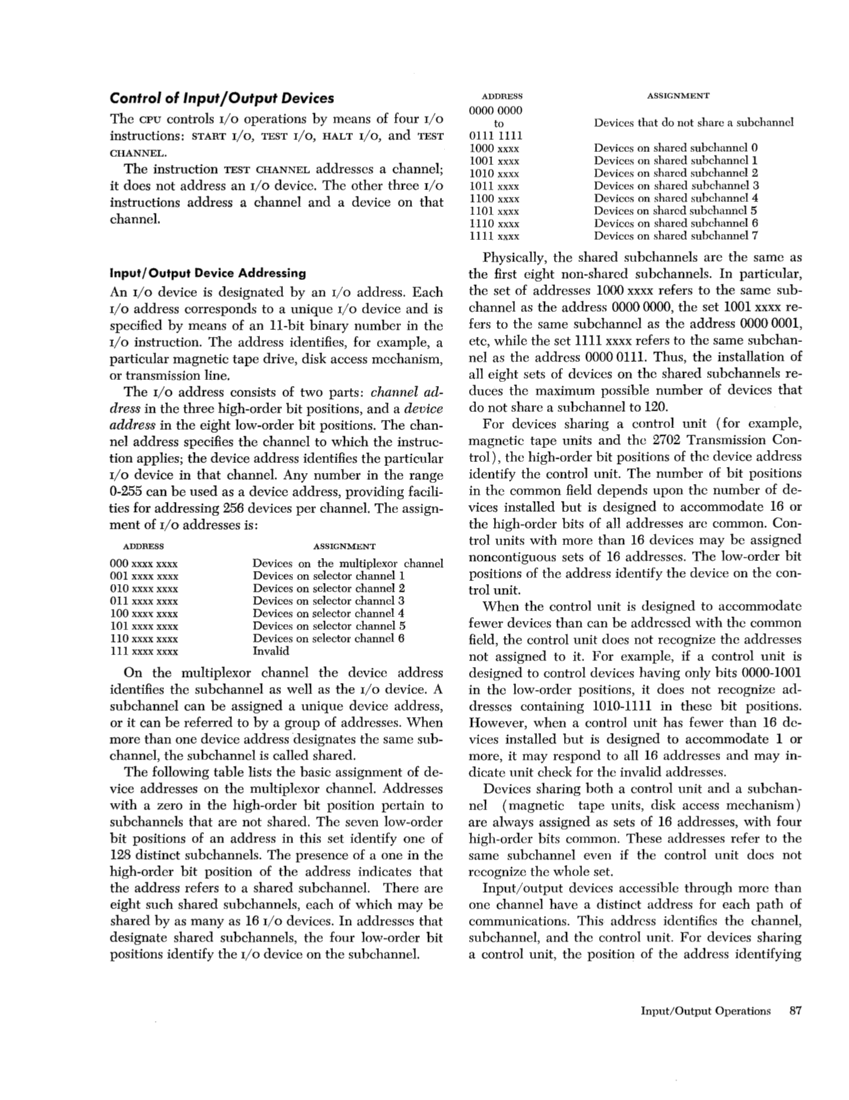

ment ofI/O addresses is:

ADDRESS000 xxxx xxxx 001 xxxx xxxx 010 xxx x xxxx 011. xxxx xxxx

1.00 xxxx xxxx 101 xxx x xxxx

110 xxxx xxxx

111 xxxx xxxx

ASSIGNMENT

Devices on the multiplexor channel

Devices on selector channel 1

Devices on selector channel 2

Devices on selector channel 3

Devices on selector channel 4

Devices on selector channel 5

Devices on selector channel 6

InvalidOn the multiplexor channel the device address

identifies the su bchannel as well as theI/O device. A

subchannel can be assigned a unique device address,

or it can be referred to by a group of addresses. When

more than one device address 'designates the same sub

channel, the subchannel is called shared.

The following table lists the basic assignment of de

vice addresses on the multiplexor channel. Addresses

with a zero in the high-order bit position pertain to

subchannels that are not shared. The seven low-order

bit positions of an address in this set identify one of

128 distinct subchannels. The presence of a one in the

high-order bit position of the address indicates that

the address refers to a shared sub channel. There are

eight such shared subchannels, each of which may be

shared by as many as 16I/O devices. In addresses that

designate shared subchannels, the four low-order bit

positions identify theI/O device on the subchannel. ADDRESS 00000000 to 0111 1111 1000 xxxx 1001 xxxx 1.010 xxxx 1011 xxxx 1100 xxxx 1101. xxxx 1110 xxxx

1111 xxxxASSIGNMENT Devices that do not share a subchannel

Devices on shared subchanncl0 Devices on shared subchannel 1

Devices on shared subchanncl 2

Devices on shared subchannel 3

Devices on shared subchannel 4

Devices on shared subchannel 5

Devices on shared subchanncl 6

Devices on shared subchannel 7Physically, the shared subchannels are the same as

the first eight non-shared subchannels. In particular,

the set of addresses 1000 xxxx refers to the same sub

channel as the address00000000, the set 1001 xxxx re

fers to the same sub channel as the address0000 0001, etc, while the set 1111 xxxx refers to the same subchan

nel as the address00000111. Thus, the installation of

all eight sets of devices on the shared subchannels re

duces the maximum possible number of devices that

do not share a subchannel to120. For devices sharing a control unit (for example,

magnetic tape units and the2702 Transmission Con trol), the high-order bit positions of the device address

identify the control unit. The number of bit positions

in the common field depends upon the number of de

vices installed but is designed to accommodate 16 or

the high-order bits of all addresses are common.Con trol units with more than 16 devices may be assigned

noncontiguous sets of 16 addresses. The low-order bit

positions of the address identify the device on the con

trol unit.

When the control unit is designed to accommodate

fewer devices than can be addressed with the common

field, the control unit does not recognize the addresses

not assigned to it. For example, if a control unit is

designed to control devices having only bits0000-1001 in the low-order positions, it does not recognize ad

dresses containing1010-1111 in these bit positions.

However, when a contra] unit has fewer than 16 de

vices installed but is designed to accommodate 1 or

more, it may respond to all 16 addresses and may in

dicate unit check for the invalid addresses.

Devices sharing both a control unit and a subchan

nel ( magnetic tape units, disk access mechanism)

are always assigned as sets of 16 addresses, with four

high-order bits common. These addresses refer to the

same sub channel even if the control unit does not

recognize the whole set.

Input! output devices accessible through more than

one channel have a distinct address for each path of

communications. This address identifies the channel,

sub channel, and the control unit. For devices sharing

a control unit, the position of the address identifying

Input/Output Operations 87

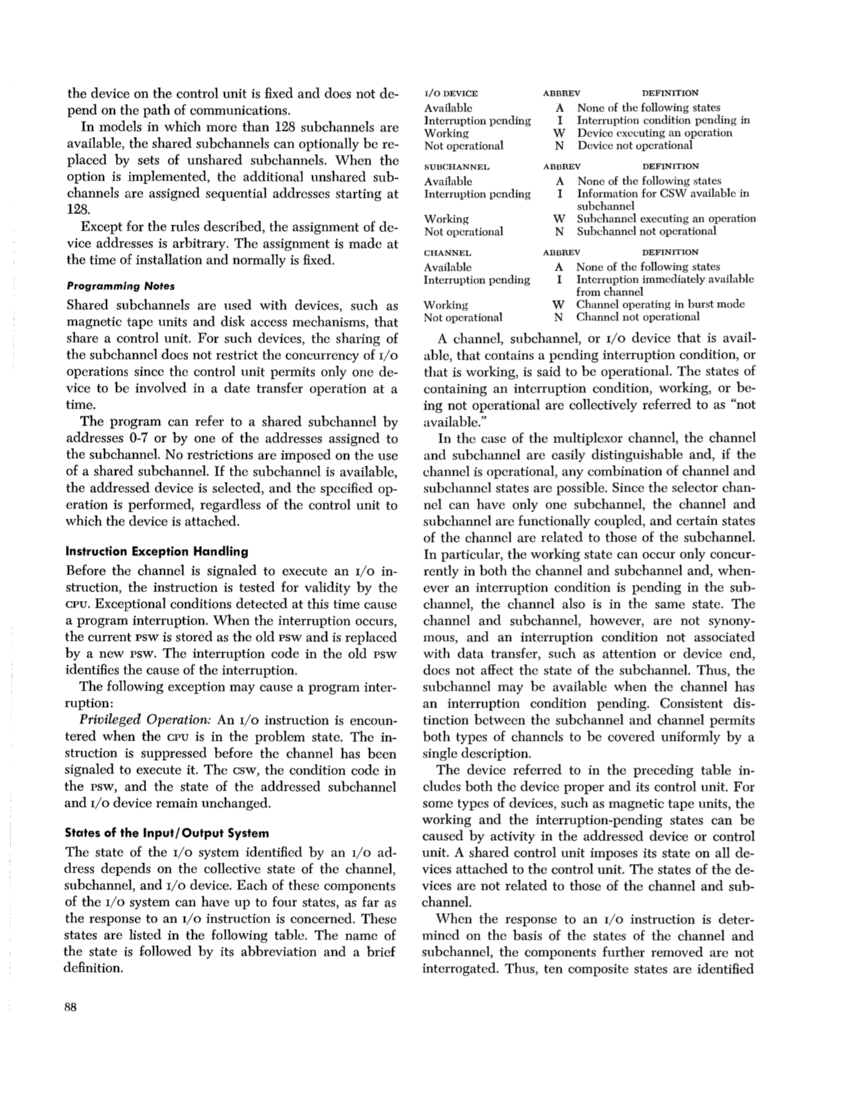

The

The instruction

it does not address an

channel.

An

specified by means of an II-bit binary number in the

particular magnetic tape drive, disk access mcchanism,

or transmission line.

The

dress in the three high-order bit positions, and a device

address in the

nel address specifies the channel to which the instruc

tion applies; the device address identifies the particular

ties for addressing 256 devices per channel. The assign

ment of

ADDRESS

1.

11

111 xxxx xxxx

ASSIGNMENT

Devices on the multiplexor channel

Devices on selector channel 1

Devices on selector channel 2

Devices on selector channel 3

Devices on selector channel 4

Devices on selector channel 5

Devices on selector channel 6

Invalid

identifies the su bchannel as well as the

subchannel can be assigned a unique device address,

or it can be referred to by a group of addresses. When

more than one device address 'designates the same sub

channel, the subchannel is called shared.

The following table lists the basic assignment of de

vice addresses on the multiplexor channel. Addresses

with a zero in the high-order bit position pertain to

subchannels that are not shared. The seven low-order

bit positions of an address in this set identify one of

128 distinct subchannels. The presence of a one in the

high-order bit position of the address indicates that

the address refers to a shared sub channel. There are

eight such shared subchannels, each of which may be

shared by as many as 16

designate shared subchannels, the four low-order bit

positions identify the

1111 xxxx

Devices on shared subchanncl

Devices on shared subchanncl 2

Devices on shared subchannel 3

Devices on shared subchannel 4

Devices on shared subchannel 5

Devices on shared subchanncl 6

Devices on shared subchannel 7

the first eight non-shared subchannels. In particular,

the set of addresses 1000 xxxx refers to the same sub

channel as the address

fers to the same sub channel as the address

nel as the address

all eight sets of devices on the shared subchannels re

duces the maximum possible number of devices that

do not share a subchannel to

magnetic tape units and the

identify the control unit. The number of bit positions

in the common field depends upon the number of de

vices installed but is designed to accommodate 16 or

the high-order bits of all addresses are common.

noncontiguous sets of 16 addresses. The low-order bit

positions of the address identify the device on the con

trol unit.

When the control unit is designed to accommodate

fewer devices than can be addressed with the common

field, the control unit does not recognize the addresses

not assigned to it. For example, if a control unit is

designed to control devices having only bits

dresses containing

However, when a contra] unit has fewer than 16 de

vices installed but is designed to accommodate 1 or

more, it may respond to all 16 addresses and may in

dicate unit check for the invalid addresses.

Devices sharing both a control unit and a subchan

nel ( magnetic tape units, disk access mechanism)

are always assigned as sets of 16 addresses, with four

high-order bits common. These addresses refer to the

same sub channel even if the control unit does not

recognize the whole set.

Input! output devices accessible through more than

one channel have a distinct address for each path of

communications. This address identifies the channel,

sub channel, and the control unit. For devices sharing

a control unit, the position of the address identifying

Input/Output Operations 87