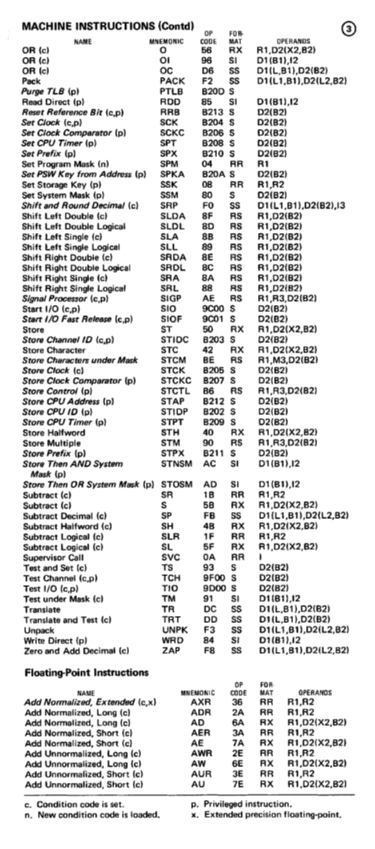

Pack

NAME

56 RX

Read Direct (p)

Reset Reference Bit (c,p)

Set Clock (c,p)

Set Clock Comparator (p)

Set

Set Prefix (p)

Set PSW Key from Address (p)

Shift and Round Decimal (c)

Signal Processor (c,p)

Start

Store Characters under Mask

Store Clock (c)

Store Clock Comparator (p)

Store Control (p)

Store

Store

Store

Store Then AND System

Mask (p)

Store Then

Test Channel (c,p)

Test

Test under Mask (c)

Translate

Translate and Test (c)

Unpack

Write Direct (p)

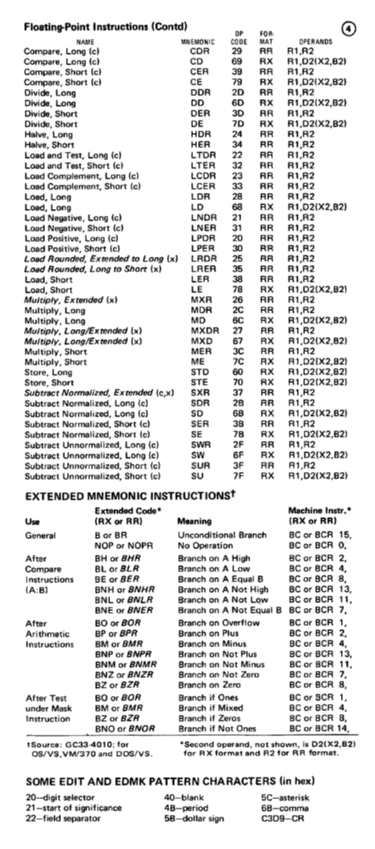

Add Normalized, Extended (c,x)

Add Normalized, Long (c)

Add Normalized, Long (c)

Add Normalized,

Add Normalized,

Add Unnormalized, Long (c)

Add Unnormalized, Long (c)

Add

Add Unnormalized,

n. New condition code is loaded.

PTL8

TR

TRT

UNPK

88

8E

8A R5

88

8E

8211 5

AC

58 RX

F8

1F RR

93 5

R1,02(82)

R1,02(82)

R1,02(82)

R1,02(82)

R1,02(82)

R1,02(82)

R1,R3,02(82)

1,02(X2,82)

R1,M3,02(82)

1,02(X2,82)

R1,R3,02(82)

R1,02(X2,82)

R1,R2

R

AER

AE

AWR

AW

AUR

AU

36 RR

2A RR

6A RX

3A RR

7A RX

2E RR

6E RX

3E RR

7E RX

R1,R2

R

R1,02(X2,82)

p. Privileged instruction.

x. Extended precision floating-point.