and controlled by information with two types of

formats: instructions and commands. Instructions

are decoded by the

by the channels and

more

form a channel program. Both instructions and

commands are fetched from main storage and are

common to all types of

modifier bits in the command code may specify

device-dependent conditions for the execution of a

data-transfer operation at the device.

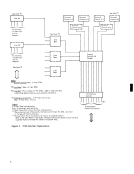

The

with the

identifies the channel and the device, and causes the

channel to fetch the channel-address word (CAW)

from a fixed location in main storage. The format

for the CAW is:

Command Address

o 3 4 78 31

The CAW contains the protection key and designates

the location in main storage from which the channel

subsequently fetches the first channel-command

word (CCW). The CCW specifies the command to be

executed and the storage area, if any, to be used.

The format for the CCW is:

o

Command

Code

78

Data Address

31

Count

63

If the subchannel associated with the addressed

select the

device to all control units attached to the channel.

The control unit that recognizes the address connects

itself logically to the channel and responds to its

selection by returning its address. The channel

subsequently sends the command-code part of the

CCW

with a status byte indicating whether it can execute

the command.

DETAILED

the

other device operating in burst mode.

At this time, the execution of

inated. The results of the attempt to initiate the

execution of the command are indicated by setting

the condition code in the program -status word (PSW) ,

and, under certain conditions, by storing pertinent

information in the channel-status word (CSW).

If the operation is initiated at the device and its

execution involves transfer of data, the subchannel is

set up to respond to service requests from the device

and assumes further control of the operation. In the

case of operations that do not require any data to be

transferred to or from the device, the device may

signal the end of the operation immediately on

receipt of the command code.

An

one storage area, designated by a single CCW, or to

a number of noncontiguous storage areas. In the

latter case, a list of CCW's is used for execution of

the

storage area, and the

flag in the CCW and causes the channel to fetch

another CCW upon the exhaustion or filling of the

storage area designated by the current CCW. The

storage area designated by a CCW fetched on data

chaining pertains to the

progress at the

when a new CCW is fetched. Provision is made in

the CCW format for the programmer to specify that,

when the CCW is decoded, the channel request an

notifying the

gressed to a particular CCW in the channel program.

Termination of the

indicated by two conditions: Channel End and Device

End. The Channel End condition indicates that the

associated with the operation and no longer needs

channel facilities. The Device End signal indicates

that the

always occurs concurrently with the Channel End

condition.

The conditions signaling the termination of an

program by

cause storing the

information concerning execution of the operation.

At the time the Channel End/Device End condition

is generated, the channel identifies the program the

11