The Exclusive OR function

(v-)

requires no coincidence of bits to obtain an output.

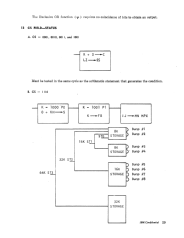

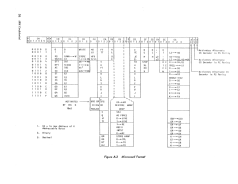

13 CS FIELD-STATUS

A. CS

=

0001, 0010, 0011, and 1001

- R

+

D-C

LZ-S5

Must be tested in the same cycle as the arithmetic statement that generates the condition.

B. CS

=

1110

-

K

=

lOOO'PO

K

=

1001

PI

o

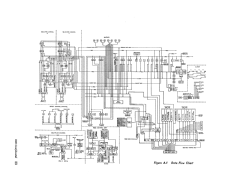

+ KH--S

K-FB

SIL.

16K SLL

32K

SR

64K S

11..

IJ -MN MPX

8K

STORAGE

8K

STORAGE

16K

STORAGE

32K

STORAGE

g

B

g

g

Bump #1

Bump #2

Bump

#3

Bump

#4

Bump

#5

Bump #6

Bump

#7

Bump

#8

IBM Confident;t"

29