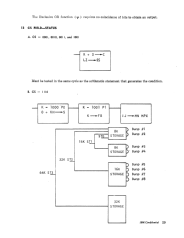

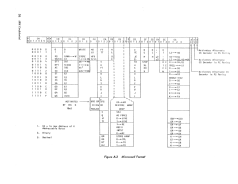

REA 0 W R I T E REA 0 COMPUTE

W R I T E

TI T2 T3 T4 Tl T2 T3 T4 Tl T2 T3 T4 T1 T2 T3

T4 TI T2

T3

T4

I---

r-----

WR I TE CALL --

I---

r---

SET MN AND READ CALL

----

MN GOOD __

-§}

I.J

STROBE SET __

850-H I-

1100

I I

R GOOD -_

L

U

I---

r---

r---

~

SET AB __

--

ADD ANSWER GOOD

600-

H I

r

r

r

ADD PARITY GOOD

793-

W-

I I

,--

I

~

r---

I---

SET DESTlNATlON __

r--

I---

~

r--

SET

ROSAR---

-J~~

ROSAR GOOD __

U

W U U

r--

I---

ROSAR GO_

SALS GOOD __

600-

r-L

U--

780

L

U

L

U

L

U

L

U

.-

I---

~

I--- I---

SET CONTROL REG __

-

--l}-

CONTROL REG GOOD--

100

U

W

U

U

ALLOW WR I TE --

CPU READ __

--

600-H

780-

H l

CPU WRI TE --

780 -

H

600-I-t

r

,

Figure A-3 Timing Chart