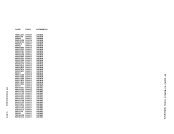

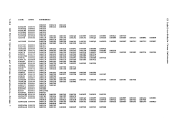

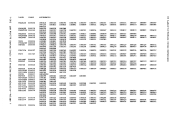

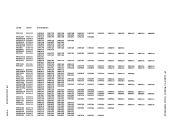

The soft recording subroutine performs two basic functions: • Formats a machine check record and calls D!KIOE!C to record the error

on the error recording cylinder.• Maintains the threshold for processor retry and ECC errors and

switchesfrom recording to quiet mode when the threshold value is

exceeded. To accomplish this, a counter is maintainedby D!K!CH for

successful processor retry and corrected Beeevents~ ~~~§§2~ R~!~I Rg£2~di~ Mo~g: Recording mode (bit 4 of control

register 14 set to one) is the initialized state, and normal operating

state ofVK/370 for processor retry errors. Recording mode may also be

enteredby use of the CP SET command. When 12 soft machine checks have

occurred, the soft recording subroutine switches the processorfrom recording mode to quiet mode. For the purpose of model-independent implementation this is accomplished by setting bit 4 of control register

14 to zero.. Because in quietmode no soft machine check interruptions

occur, a switchfroa quiet mode to recording mode can be made by issuing

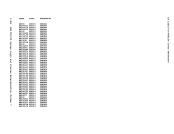

theSET MODE RETRYIKAIN RECORD command. While in recording mode, corrected CPU RETRYIKAIN reports are formatted and recorded on the V8/370 error recording cylinder, but the primary systems operator is not informed of these occurrences. Proc~§§2~ R~!~I Quig! ~odg: Quiet mode (bit 4 of control register 14 set

to0) can be entered in one of two ways: (1) when 12 soft machine checks have occurred, or (2) when the SET !ODE RETRY QUIET command is

executedby a class F user. In this mode, both processor retry and ECC

reporting are disabled. The processor remains in quietmode until the

nextsystem IPL (warm start or cold start) occurs or a SET !ODE RETRYI!AIN RECORD command is executed by a class F user. SET KODE 81IN is treated as invalid on a 3031, 3032, or 3033 processor.

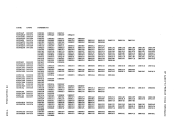

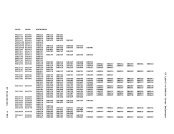

ECCR~£2rd1~g ~odg§: To achieve model-independent support, RKS does not

set a specificmode for ECC recording. The mode in which ECC recording

is initialized depends upon the hardware design for each specific

processormodel. For the IBM System/370 Models 135, 135-3, 138, 145,

145-3, 148, 158, 168,3031, 3032, and 3033, the hardware-initialized

state (therefore thenormal operational state for V!/370) is quiet mode. For the IB! System/370 Models 155 II and 165 II, the hardware

initialized state (the normal operational state forV!/370) is record mode. An automatic restart incident due to a V8/370 failure does not

reset the ECC recordingmode in effect at the time of failure.

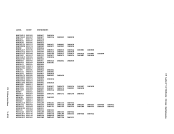

The changefrom record to quiet mode for ECC recording can be

initiated in either of the followingways: (1) by issuing the SET KODE {MAINIRETRY} QUIET co.mand, or (2) automatically whenever 12 soft machine checks have occurred. For the purpose of model-independent

implementation, this occursby setting bit 4 of control register 14 to

zero.

The changefrom quiet to record mode for ECC recording can be

accomplishedby use of the SET KODE KAIN RECORD com.and. This recording mode option is for use by maintenance personnel only. It should be

noted that processor retry is placed in recordingmode if it is not in

that state when theSET MODE !AIN RECORD command is issued. While in recording mode, corrected Eee reports are formatted and

recorded on the error recording cylinder, but theprimary systems operator is not informed of these incidents.

1-156IBM VM/370 System Logic and Problem Determination--Volume 1

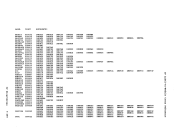

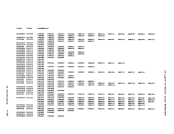

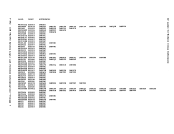

on the error recording cylinder.

switches

exceeded. To accomplish this, a counter is maintained

successful processor retry and corrected Bee

register 14 set to one) is the initialized state, and normal operating

state of

entered

occurred, the soft recording subroutine switches the processor

14 to zero.. Because in quiet

occur, a switch

the

to

executed

reporting are disabled. The processor remains in quiet

next

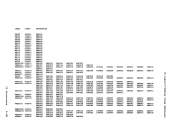

ECC

set a specific

is initialized depends upon the hardware design for each specific

processor

145-3, 148, 158, 168,

state (therefore the

initialized state (the normal operational state for

reset the ECC recording

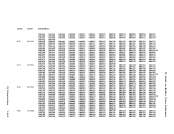

The change

initiated in either of the following

implementation, this occurs

zero.

The change

accomplished

noted that processor retry is placed in recording

that state when the

recorded on the error recording cylinder, but the

1-156