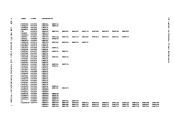

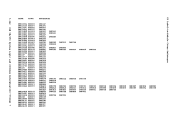

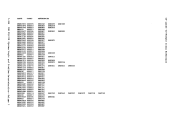

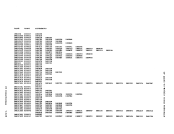

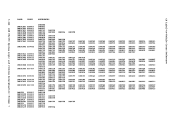

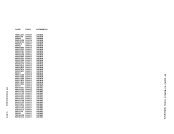

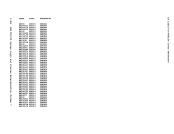

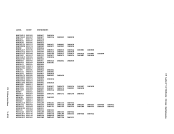

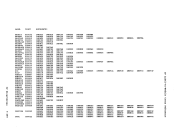

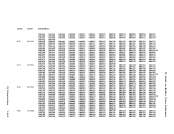

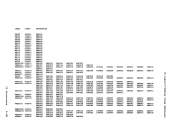

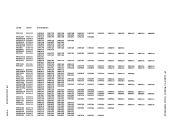

and for:

Console

Local

Solicited device end

Channel error

Monitor tape

Dedicated device error -

R

ecoverab

Reason for

Bor.al paging

Supervisor

unit record, virtual spooling

Ignored -

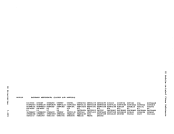

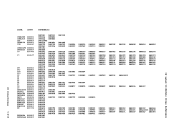

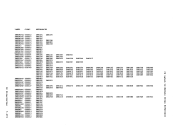

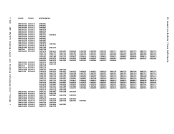

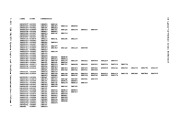

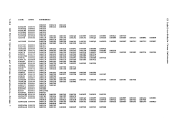

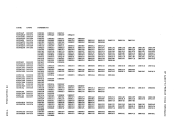

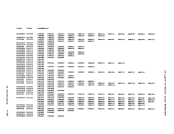

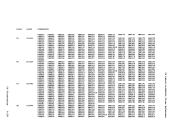

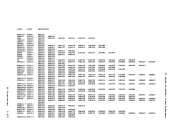

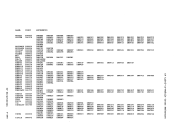

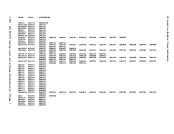

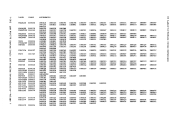

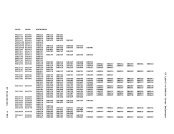

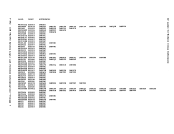

Figure 14.

control to

routine sets an invalid interruption code and reflects the interruption

to the virtual aachine. For the privileged instructions