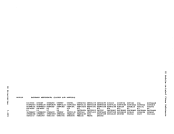

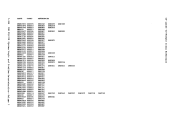

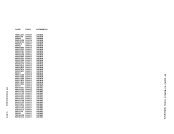

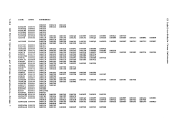

data conversion and control block scanning and verification.

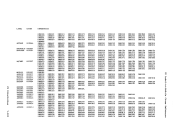

the routines are linked to via the BALR option of the CALL

aake use use of the

routine.

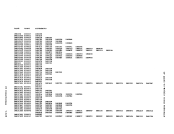

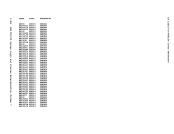

control registers (logical registers since the number that are active

depends on the features installed in the

are addressable for loading and storing

for normal virtual machines, and for processing

require the full set of registers (for

operating systems for

control registers other than control register zero, can request the full

set of 16 registers

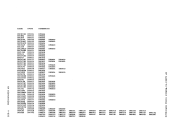

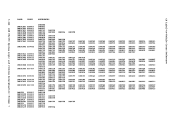

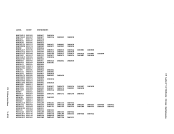

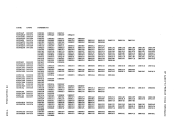

the control registers, requires the

features are expanded timer support of the

comparator, etc., the virtual relocate mode and its instructions, RRB,

LRA,

conventions when they are designed and coded:

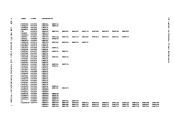

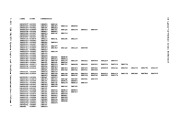

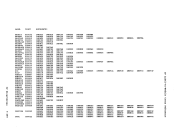

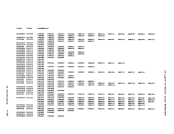

return to its caller by

8 CALL linkage.

point to locations within itself or within other pageable

themselves. The only exceptions are address constant literals

generated as the result of calls to other modules (because these

addresses are dynaaically relocated at execution

resolved

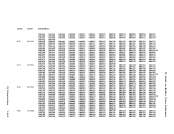

and a pageable module that locks itself into storage. In practice,

this restriction

routine

address in register 15 for a CALL may not be generated