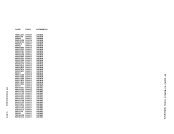

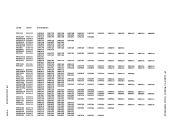

II, 168,

168,

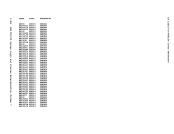

failure is reported via a degradation report machine check interruption.

system initialization by setting bit 5 of control register

a machine check interruption occurs that indicates high-speed buffer or

DLAT damage,

the error recording cylinder, informs the primary systems operator of

the failure, and returns control to the system to continue

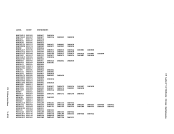

The termination subroutine is given control if a hard machine check

interruption occurs while

check interruption. Note that soft error reporting is disabled for the

entire time that

An analysis is performed of the machine check interruption code of

the first error to determine if it was a soft error. If it was, the

first error is recorded, the system status is restored and control is

restored to the point where the first error occurred. If the first

error was a hard error, the operator communication subroutine is given

control to issue a message directly to the system operator, and to

terminate CP operation.

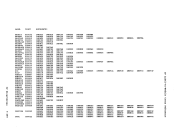

The channel check handler (CCH) aids the

of the occurrence of channel errors.

CCH receives control from the

check, channel control check, or interface control check occurs. CCH

produces an

representative

co.mand.

operator each

routine status examination following an

check, an

cylinder.

constructing an

that

address, etc.), then CP operation is terminated. CP termination causes

processor in a disabled wait state with a recognizable wait code in the

processor instruction counter.

CP Introduction 1-151