By TNL:

and,

code.

considered as binary unsigned quantities, with all

codes valid. The operation proceeds left to right and

ends as soon as an inequality is found or

the fields is reached.

When part of an operand in CL or

nated in an inaccessible location but the operation

can

parts, it is unpredictable whether the access excep

tion for the inaccessible part is recognized.

Resulting Condition Code:

o

1 First operand is

3 -

operand 1, CLI and CLC)

The

bits

variable-length operation, comparison may extend to

field lengths of 256 bytes. The operation may be

used to compare unsigned packed decimal fields or

alphameric information in any code that has a collat

ing

nary values. For example, EBCDIC has a collating

The second operand is compared with the first oper'-

cated in the condition code.

The contents of the M3 field, bit positions 12-15,

are

right, correspond one for one with the four bytes,

left to right, of the general register designated by the

R 1 field. The byte positions corresponding to ones in

the mask are considered as a contiguous field and

126

are compared with the second operand. The second

operand is a contiguous field in storage, starting at

the second-operand address and equal in length to

the number of ones in the mask. The bytes in the

general register corresponding to zeros in the mask

do not participate in the operation.

The comparison is performed with the operands

considered as binary unsigned quantities, with all

codes valid. The operation proceeds left to right.

When the mask is not zero, exceptions associated

with storage-operand access are recognized only for

the number of bytes specified by the mask. Howev

er, when part of the designated storage operand is in

an inaccessible location but the operation can be

completed by using the accessible operand parts, it is

unpredictable whether the exception for the inaccess

ible part is indicated. When the mask is zero, access

exceptions are recognized for one byte.

o Selected bytes are equal, or mask is zero

1 Selected field of

2 Selected field of first operand is high

3 -

Program Exceptions:

Access (fetch, operand 2)

Compare Logical Long

CLCL Rl,R2 [RR]

The first operand is compared with the second oper

and, and the result is indicated in the condition

code. The shorter operand is considered extended

with the padding character.

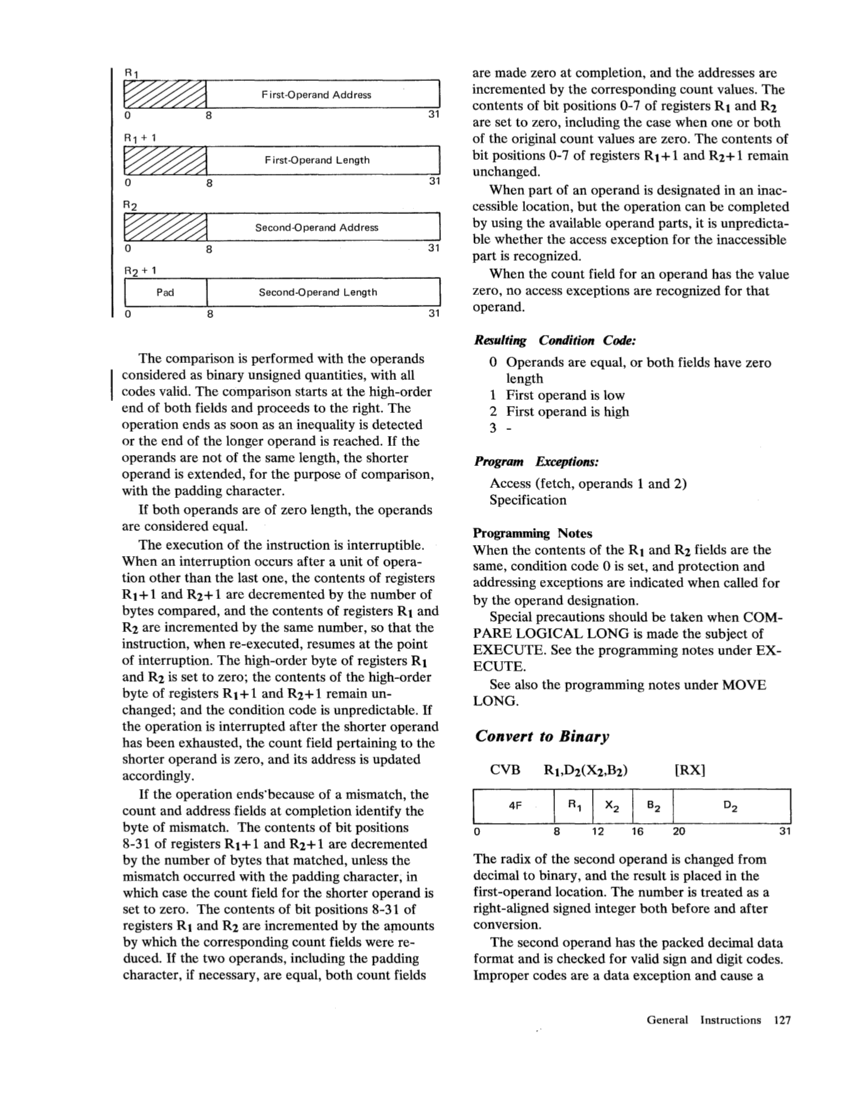

The Rl and R2 fields each specify an even-odd

pair of general registers and must designate an even

numbered register; otherwise, a specification excep

tion is recognized.

The location of the leftmost byte of the first oper

and and second operand is designated by bits 8-31

of the general registers specified by the Rl and R2

fields, respectively. The number of bytes in the first

operand and second-operand locations is specified

by bits 8-31 of the general registers having addresses

Rl + 1 and R2+ 1, respectively. Bit positions

register R2 + 1 contain the padding character. The

contents

R 1 + 1 are ignored.

Graphically, the contents of the registers just de

scribed are as follows: