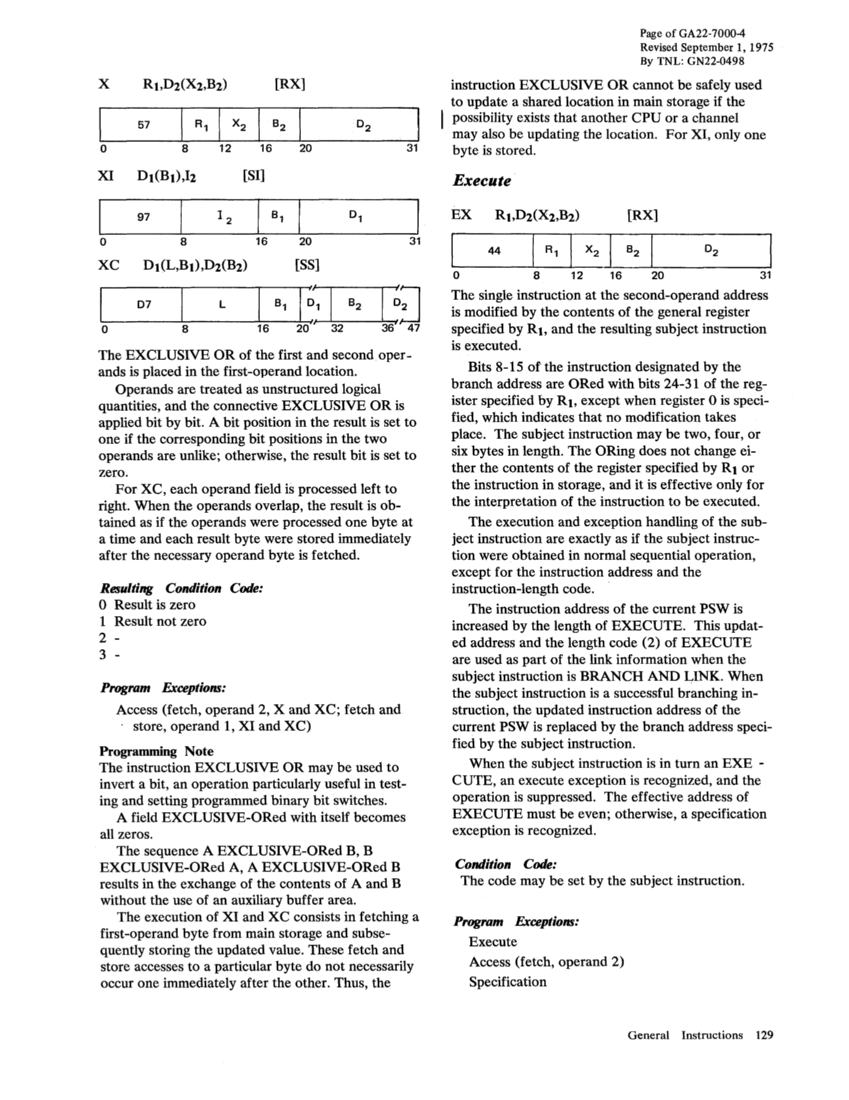

x

o

XI

o

xc

o

8 12 1620 [SI]

97

8

Dl(L,Bl),D2(B2)

07 L

8

1620 [SS]

31

31

The EXCLUSIVEOR of the first and second.oper

ands is placed in the first-operand location.Operands are treated as unstructured logical

quantities, and the connective EXCLUSIVEOR is

applied bit by bit. A bit position in the result is set to

one if the corresponding bit positions in the two

operands are unlike; otherwise, the result bit is set to

zero.

For XC, each operand field is processed left to

right. When the operands overlap, the result is ob

tained as if the operands were processed one byte at

a time and each result byte were stored immediately

after the necessary operand byte is fetched.

Resulting Condition Code:

o Result is zero

1 Result not zero

2 -

3 -

Program Exceptions:

Access (fetch, operand 2, X and XC; fetch and

. store, operand 1, XI and XC)

Programming Note

The instruction EXCLUSIVEOR may be used to

invert a bit, an operation particularly useful in test

ing and setting programmed binary bit switches.

A fieldEXCLUSIVE-ORed with itself becomes

all zeros.

The sequence AEXCLUSIVE-ORed B, B EXCLUSIVE-ORed A, A EXCLUSIVE-ORed B

results in the exchange of the contents of A and B

without the use of an auxiliary buffer area.

The execution of XI and XC consists in fetching a

first-operand byte from main storage and subse

quently storing the updated value. These fetch and

store accesses to a particular byte do not necessarily

occur one immediately after the other. Thus, the

Page of GA22-7000-4

Revised September 1, 1975

By TNL: GN22-0498

instruction EXCLUSIVEOR cannot be safely used

to update a shared location in main storage if the

possibility exists that anotherCPU or a channel

may also be updating the location. For XI, only one

byte is stored.

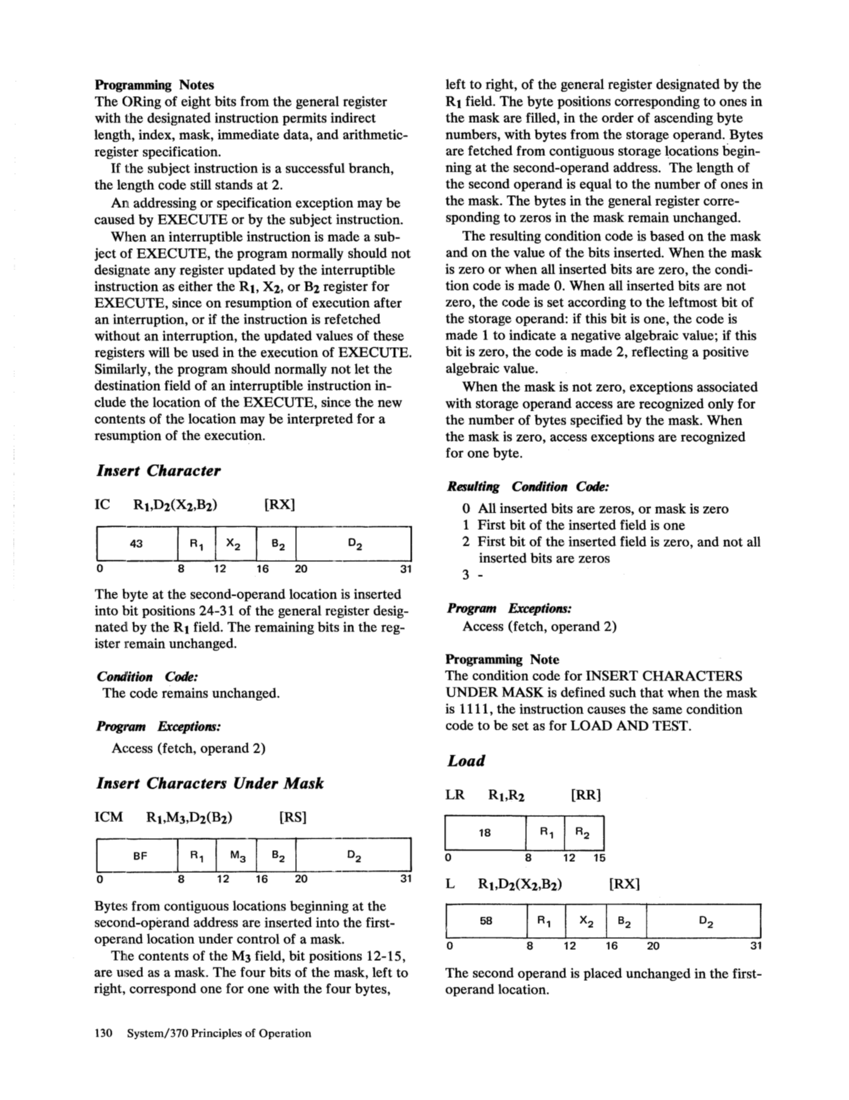

Execute

44

o 8 12 1620 31

The single instruction at the second-operand address

is modified by the contents of the general register

specified by Rl, and the resulting subject instruction

is executed.

Bits 8-15 of the instruction designated by the

branch address areORed with bits 24-31 of the reg

ister specified by Rl, except when register0 is speci

fied, which indicates that no modification takes

place. The subject instruction may be two, four, or

six bytes in length. TheORing does not change ei

ther the contents of the register specified by Rl or

the instruction in storage, and it is effective only for

the interpretation of the instruction to be executed.

The execution and exception handling of the sub

ject instruction are exactly as if the subject instruc

tion were obtained in normal sequential operation,

except for the instruction address and the

instruction-length code.

The instruction address of the currentPSW is

increased by the length of EXECUTE. This updat

ed address and the length code (2) of EXECUTE

are used as part of the link information when the

subject instruction is BRANCH AND LINK. When

the subject instruction is a successful branching in

struction, the updated instruction address of the

currentPSW is replaced by the branch address speci

fied by the subject instruction.

When the subject instruction is in turn an EXE -

CUTE, an execute exception is recognized, and the

operation is suppressed. The effective address of

EXECUTE must be even; otherwise, a specification

exception is recognized.

Condition Code:

The code may be set by the subject instruction.Program Exceptions:

Execute

Access (fetch, operand 2)

Specification

General Instructions 129

o

XI

o

xc

o

8 12 16

97

8

Dl(L,Bl),D2(B2)

07 L

8

16

31

31

The EXCLUSIVE

ands is placed in the first-operand location.

quantities, and the connective EXCLUSIVE

applied bit by bit. A bit position in the result is set to

one if the corresponding bit positions in the two

operands are unlike; otherwise, the result bit is set to

zero.

For XC, each operand field is processed left to

right. When the operands overlap, the result is ob

tained as if the operands were processed one byte at

a time and each result byte were stored immediately

after the necessary operand byte is fetched.

Resulting Condition Code:

o Result is zero

1 Result not zero

2 -

3 -

Program Exceptions:

Access (fetch, operand 2, X and XC; fetch and

. store, operand 1, XI and XC)

Programming Note

The instruction EXCLUSIVE

invert a bit, an operation particularly useful in test

ing and setting programmed binary bit switches.

A field

all zeros.

The sequence A

results in the exchange of the contents of A and B

without the use of an auxiliary buffer area.

The execution of XI and XC consists in fetching a

first-operand byte from main storage and subse

quently storing the updated value. These fetch and

store accesses to a particular byte do not necessarily

occur one immediately after the other. Thus, the

Page of GA22-7000-4

Revised September 1, 1975

By TNL: GN22-0498

instruction EXCLUSIVE

to update a shared location in main storage if the

possibility exists that another

may also be updating the location. For XI, only one

byte is stored.

Execute

44

o 8 12 16

The single instruction at the second-operand address

is modified by the contents of the general register

specified by Rl, and the resulting subject instruction

is executed.

Bits 8-15 of the instruction designated by the

branch address are

ister specified by Rl, except when register

fied, which indicates that no modification takes

place. The subject instruction may be two, four, or

six bytes in length. The

ther the contents of the register specified by Rl or

the instruction in storage, and it is effective only for

the interpretation of the instruction to be executed.

The execution and exception handling of the sub

ject instruction are exactly as if the subject instruc

tion were obtained in normal sequential operation,

except for the instruction address and the

instruction-length code.

The instruction address of the current

increased by the length of EXECUTE. This updat

ed address and the length code (2) of EXECUTE

are used as part of the link information when the

subject instruction is BRANCH AND LINK. When

the subject instruction is a successful branching in

struction, the updated instruction address of the

current

fied by the subject instruction.

When the subject instruction is in turn an EXE -

CUTE, an execute exception is recognized, and the

operation is suppressed. The effective address of

EXECUTE must be even; otherwise, a specification

exception is recognized.

Condition Code:

The code may be set by the subject instruction.

Execute

Access (fetch, operand 2)

Specification

General Instructions 129