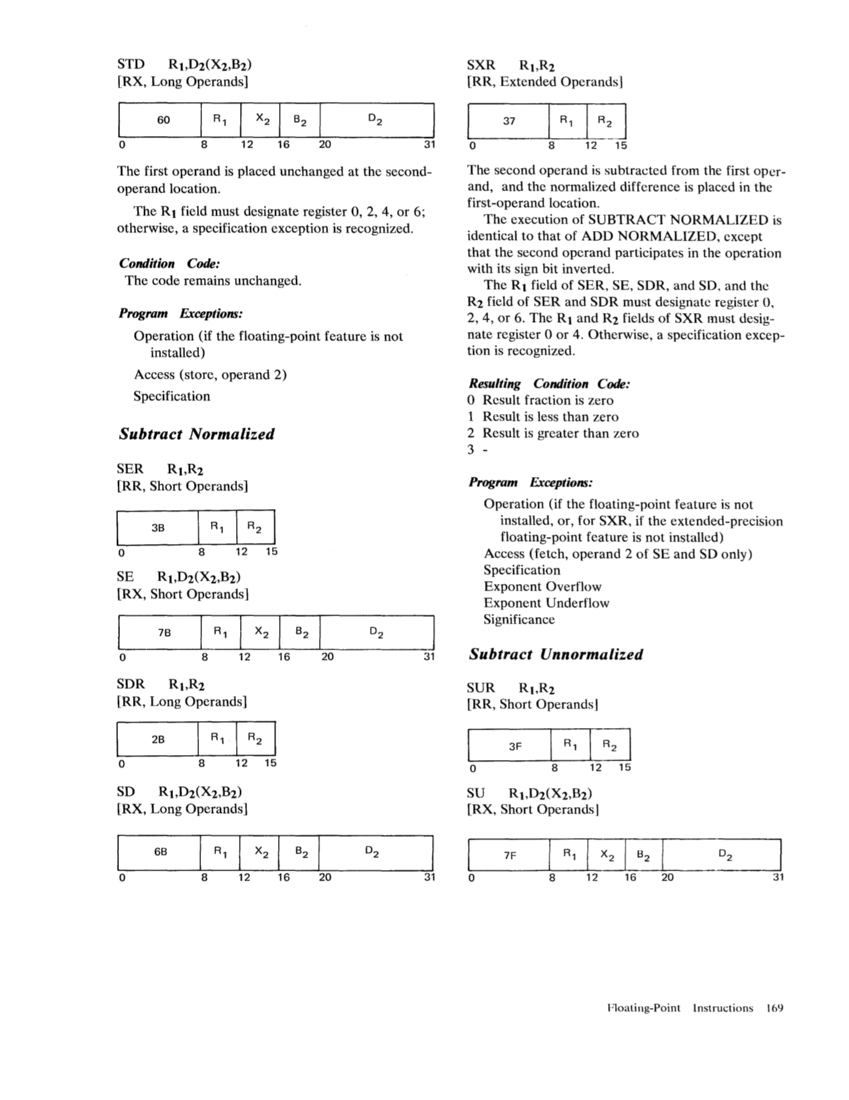

STD Rl,D2(X2,B2)

[RX, LongOperands] 60 o 8 12 16 20 31

The first operand is placed unchanged at the second

operand location.

The Rl field must designate register0, 2, 4, or 6;

otherwise, a specification exception is recognized.

Condition Code:

The code remains unchanged.

Program Exceptions:Operation (if the floating-point feature is not

installed)

Access (store, operand 2)

Specification

Subtract Normalized

SER Rl,R2

[RR, ShortOperands] 38

o 8 12 15

SE Rl,D2(X2,B2)

[RX, ShortOperands] SDR Rl,R2

[RR, LongOperands] 28

o 8 12 15

SD R 1 ,D2(X2,B2)

[RX, LongOperands] 68

o 8 12 1620 31

SXR Rl,R2

[RR, ExtendedOperands] 37

o

The second operand is subtracted from the firstOPer and, and the normalized difference is placed in the

first-operand location.

The execution ofSUBTRACT NORMALIZED is

identical to that of ADDNORMALIZED, except

that the second operand participates in the operation

with its sign bit inverted.

The Rl field of SER, SE, SDR, andSO, and the

R2 field of SER and SDR must designate register0, 2,4, or 6. The Rl and R2 fields of SXR must desig

nate register0 or 4. Otherwise, a specification excep

tion is recognized.

Resulting Condition Code:

o Result fraction is zero

1 Result is less than zero

2 Result is greater than zero

3 -

Program Exceptions:Operation (if the floating-point feature is not

installed, or, for SXR, if the extended-precision

floating-point feature is not installed)

Access (fetch, operand 2 of SE andSO only)

Specification

ExponentOverflow Exponent Underflow Significance

Subtract UnnormalizedSUR Rl,R2

[RR, ShortOperands J

3FI R, I :J o 8 12 15 SU Rl,D2(X2,B2)

[RX, ShortOperands j L- ___ 7_F ____ _____ 20 31 Floating-Point Instructions 169

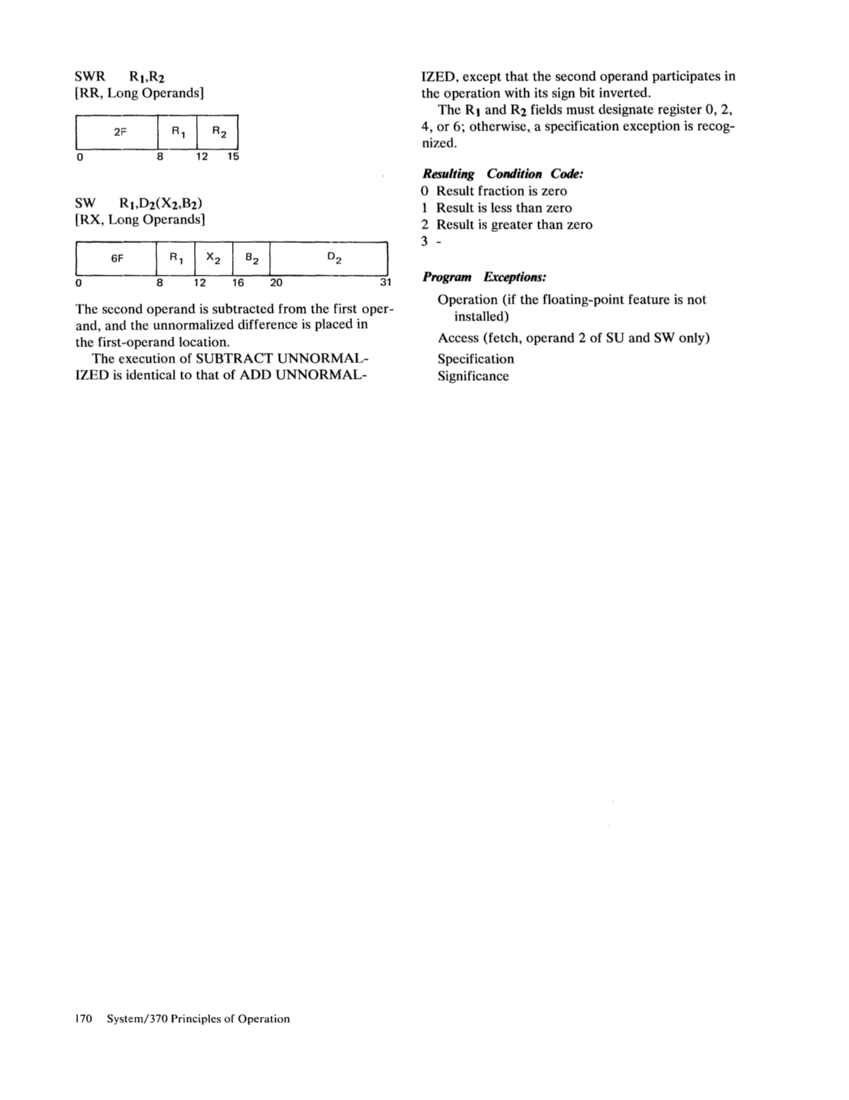

[RX, Long

The first operand is placed unchanged at the second

operand location.

The Rl field must designate register

otherwise, a specification exception is recognized.

Condition Code:

The code remains unchanged.

Program Exceptions:

installed)

Access (store, operand 2)

Specification

Subtract Normalized

SER Rl,R2

[RR, Short

o 8 12 15

SE Rl,D2(X2,B2)

[RX, Short

[RR, Long

o 8 12 15

SD R 1 ,D2(X2,B2)

[RX, Long

o 8 12 16

SXR Rl,R2

[RR, Extended

o

The second operand is subtracted from the first

first-operand location.

The execution of

identical to that of ADD

that the second operand participates in the operation

with its sign bit inverted.

The Rl field of SER, SE, SDR, and

R2 field of SER and SDR must designate register

nate register

tion is recognized.

Resulting Condition Code:

o Result fraction is zero

1 Result is less than zero

2 Result is greater than zero

3 -

Program Exceptions:

installed, or, for SXR, if the extended-precision

floating-point feature is not installed)

Access (fetch, operand 2 of SE and

Specification

Exponent

Subtract Unnormalized

[RR, Short

3F

[RX, Short