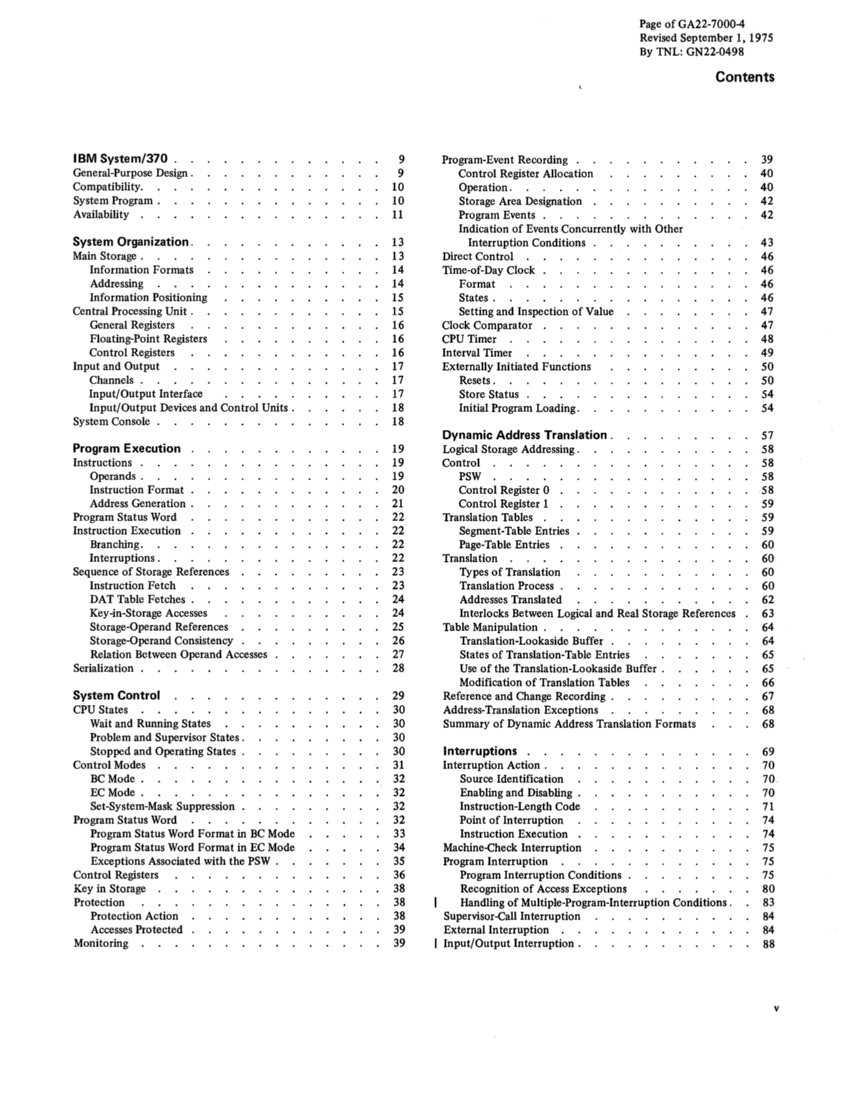

General-Purpose Design . 9

Compatibility.

Main

Information Formats 14

Addressing 14

Information Positioning 15

Central Processing

General Registers 16

Floating-Point Registers 16

Control Registers 16

Input and

Channels. 17

Input/Output Interface 17

Input/Output Devices and Control

Program Execution 19

Instructions . 19

Operands. 19

Instruction Format

Program

Instruction Execution 22

Branching. 22

Interruptions. 22

Sequence of

Instruction Fetch 23

DAT Table Fetches . 24

Key-in-Storage Accesses 24

Relation Between

Serialization . 28

BC Mode. 32

EC Mode. 32

Program

Program

Program

Exceptions Associated with the

Control Registers 36

Key in

Protection 38

Protection Action 38

Accesses Protected 39

Monitoring 39

Page

By TNL:

Program-Event Recording . 39

Control Register Allocation

Program Events . 42

Indication of Events Concurrently with

Direct Control 46

Time-of-Day Clock 46

Format 46

Clock Comparator 47

In terval Timer 49

Externally Initiated Functions

Initial Program Loading. 54

Dynamic Address Translation. 57

Logical

Control 58

Control Register

Control Register 1 59

Translation Tables 59

Segment-Table Entries 59

Page-Table Entries

Interlocks Between Logical and Real

Table Manipulation . 64

Translation-Lookaside Buffer . 64

Modification of Translation Tables 66

Reference and Change Recording . 67

Address-Translation Exceptions 68

Interruptions 69

Interruption Action.

Point of Interruption 74

Instruction Execution 74

Machine-Check Interruption 75

Program Interruption 75

Program Interruption Conditions 75

Recognition of Access Exceptions

Supervisor-Call Interruption 84

External In terruption 84

Input/Output Interruption. 88

v