The program may have zeros in the base address,

index, or displacement fields. A zero is used to indi

cate the absence of the corresponding address com

ponent. A base or index of zero implies that a zero

quantity is to be used in forming the address, regard

less of the contents of general registerO. A displace

ment of zero has no special significance. Initialization,

modification, and testing of base addresses and in

dexes can be carried out by fixed-point instructions,

or by BRANCH AND LINK, BRANCHON COUNT, or BRANCH ON INDEX instructions.

As an aid in describing the logic of the instruction

format, examples of two instructions and their related

instruction formats follow.RR Format I Add 7 9

o 78 1112 15

Execution of the ADD instruction adds the contents of

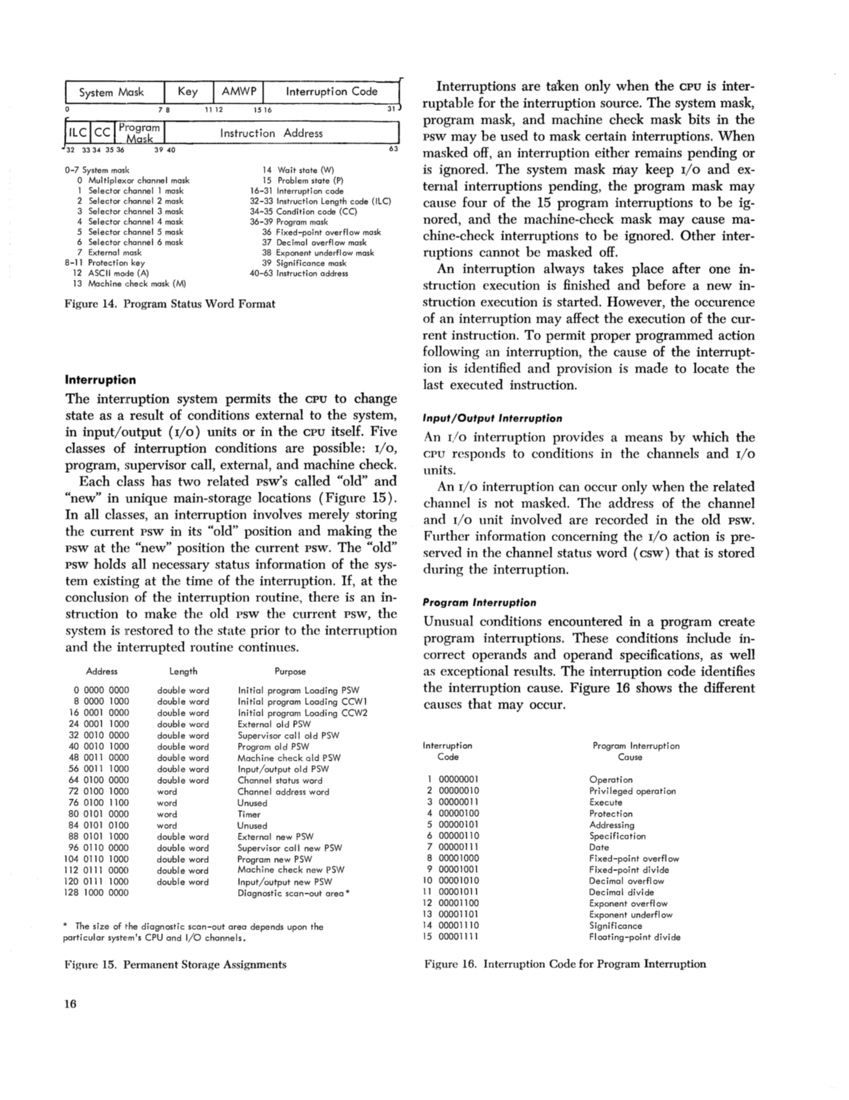

general register 9 to the contents of general register

7 and the sum of the addition is placed in general

register 7.

RX Format

Store 310 14 300 7 8 11 1 2 15 16 1 9 20 31

Execution of theSTORE instruction stores the contents

of general register 3 at a main-storage location ad

dressed by the sum of300 and the low-order 24 bits

of general registers 14 and10. Sequential Instruction Execution

Normally, the operation of theCPU is controlled by

instructions taken in sequence. An instruction is

fetched from a location specified by the current in

struction address. The instruction address is then in

creased by the number of bytes in the instruction to

address the next instruction in sequence. The instruc

tion is then executed and the same steps are repeated

using the new value of the instruction address.

Conceptually, all halfwords of an instruction are

fetched from storage after the preceding operation is

completed and before execution of the current oper

ation, even though physical storage word size and

overlap of instruction execution with storage access

may cause actual instruction fetching to be different.

Thus, it is possible to modify an instruction in storage

by the immediately preceding instruction.

A change from sequential operation may be caused

by branching, status switching, interruptions, or man

ual intervention.

Branching

The normal sequence of instructions is changed when

reference is made to a subroutine, when a two-way

choice is encountered, or when a segment of coding,

such as a loop, is to be repeated. All these tasks can

be accomplished with branching instructions.

Subroutine linkage permits not only the intro

duction of a new instruction address but also the pres

ervation of the return address and associated informa

tion.

Decision-making is generally and symmetrically

provided by the BRANCHON CONDITION instruction.

This instruction inspects a two-bit condition code that

reflects the result of a majority of the arithmetic, logi

cal, andI/O operations. Each of these operations can

set the code in anyone of four states, and the con

ditional branch can specify any selection of these four

states as the criterion for branching. For example, the

condition code reflects such conditions as nonzero,

first operand high, equal, overflow, channel busy, zero,

etc.Once set, the condition code remains unchanged

until modified by an instruction that reflects a dif

ferent condition code.

The two bits of the condition code provide for four

possible condition code settings:0, 1, 2, and 3. The

specific meaning of any setting is significant only to

the operation setting the condition code.

Loop control can be performed by the conditional

branch when it tests the outcome of address arith

metic and counting operations. For some particularly

frequent combinations of arithmetic and tests, the in

structionsBRANCH ON COUNT and BRANCH ON INDEX are

provided. These branches, being specialized, provide

increased performance for these tasks.

Program Status Word

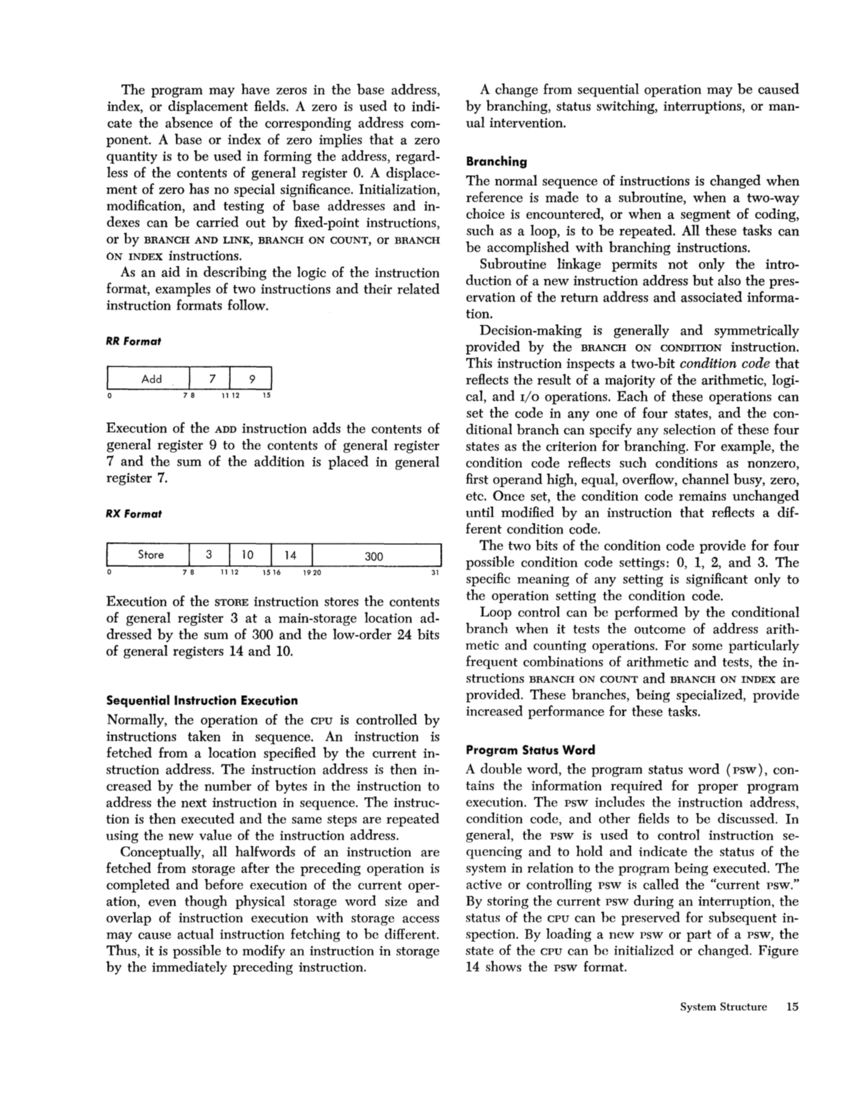

A double word, the program status word (psw), con

tains the information required for proper program

execution. The psw includes the instruction address,

condition code, and other fields to be discussed. In

general, the psw is used to control instruction se

quencing and to hold and indicate the status of the

system in relation to the program being executed. The

active or controlling psw is called the"current psw." By storing the current psw during an interruption, the

status of theCPU can be preserved for subsequent in

spection. By loading a new psw or part of a psw, the

state of theCPU can be initialized or changed. Figure

14 shows the psw format.

System Structure 15

index, or displacement fields. A zero is used to indi

cate the absence of the corresponding address com

ponent. A base or index of zero implies that a zero

quantity is to be used in forming the address, regard

less of the contents of general register

ment of zero has no special significance. Initialization,

modification, and testing of base addresses and in

dexes can be carried out by fixed-point instructions,

or by BRANCH AND LINK, BRANCH

As an aid in describing the logic of the instruction

format, examples of two instructions and their related

instruction formats follow.

o 78 1112 15

Execution of the ADD instruction adds the contents of

general register 9 to the contents of general register

7 and the sum of the addition is placed in general

register 7.

RX Format

Store 3

Execution of the

of general register 3 at a main-storage location ad

dressed by the sum of

of general registers 14 and

Normally, the operation of the

instructions taken in sequence. An instruction is

fetched from a location specified by the current in

struction address. The instruction address is then in

creased by the number of bytes in the instruction to

address the next instruction in sequence. The instruc

tion is then executed and the same steps are repeated

using the new value of the instruction address.

Conceptually, all halfwords of an instruction are

fetched from storage after the preceding operation is

completed and before execution of the current oper

ation, even though physical storage word size and

overlap of instruction execution with storage access

may cause actual instruction fetching to be different.

Thus, it is possible to modify an instruction in storage

by the immediately preceding instruction.

A change from sequential operation may be caused

by branching, status switching, interruptions, or man

ual intervention.

Branching

The normal sequence of instructions is changed when

reference is made to a subroutine, when a two-way

choice is encountered, or when a segment of coding,

such as a loop, is to be repeated. All these tasks can

be accomplished with branching instructions.

Subroutine linkage permits not only the intro

duction of a new instruction address but also the pres

ervation of the return address and associated informa

tion.

Decision-making is generally and symmetrically

provided by the BRANCH

This instruction inspects a two-bit condition code that

reflects the result of a majority of the arithmetic, logi

cal, and

set the code in anyone of four states, and the con

ditional branch can specify any selection of these four

states as the criterion for branching. For example, the

condition code reflects such conditions as nonzero,

first operand high, equal, overflow, channel busy, zero,

etc.

until modified by an instruction that reflects a dif

ferent condition code.

The two bits of the condition code provide for four

possible condition code settings:

specific meaning of any setting is significant only to

the operation setting the condition code.

Loop control can be performed by the conditional

branch when it tests the outcome of address arith

metic and counting operations. For some particularly

frequent combinations of arithmetic and tests, the in

structions

provided. These branches, being specialized, provide

increased performance for these tasks.

Program Status Word

A double word, the program status word (psw), con

tains the information required for proper program

execution. The psw includes the instruction address,

condition code, and other fields to be discussed. In

general, the psw is used to control instruction se

quencing and to hold and indicate the status of the

system in relation to the program being executed. The

active or controlling psw is called the

status of the

spection. By loading a new psw or part of a psw, the

state of the

14 shows the psw format.

System Structure 15