The sign bit is leftmost in a number. An overHow

carries into the sign-bit positionand changes the sign.

However, in algebraic shifting the sign bit does not

change even if significant high-order bits are shifted

out.

Programming Notes

Two's-complement notation is particularly suited to

address computation and multiple-precision arithmetic.

The two's-complement representation of a negative

number may be considered the sum of the integer

part of the field, taken as a positive number, and the

maximum negative number. Hence, in multiple-preci

sion arithmetic the low-order fields should be treated

as positive numbers. Also, when negative numbers are

shifted to the right, the resulting rounding, if any, is

toward minus infinity and not toward zero.

Conditic)n Code

The results of fixed-point sign-control, add, subtract,compare" and shift operations are used to set the condi

tion code in the program status word (psw). All other

fixed-point operations leave this code undisturbed.

The condition code can be used for decision-making

by subsequent branch-on-condition instructions.

The condition code can be set to reHect three types

of results for fixed-point arithmetic. For most opera

tions, the states0, 1, or 2 indicate a zero, less than

zero, or greater than zero content of the result reg

ister' while the state 3 is used when the result over

Hows.

For a comparison, the states0, 1, or 2 indicate that

the first operand is equal, low, or high.

For ADDLOGICAL and SUBTRACT LOGICAL, the codes ° and 1 indicate a zero or nonzero result register con

tent in the absence of a logical carry out of thc sign

position; the codes 2 and 3 indicate a zero or nonzero

result register content with a logical carry out of the

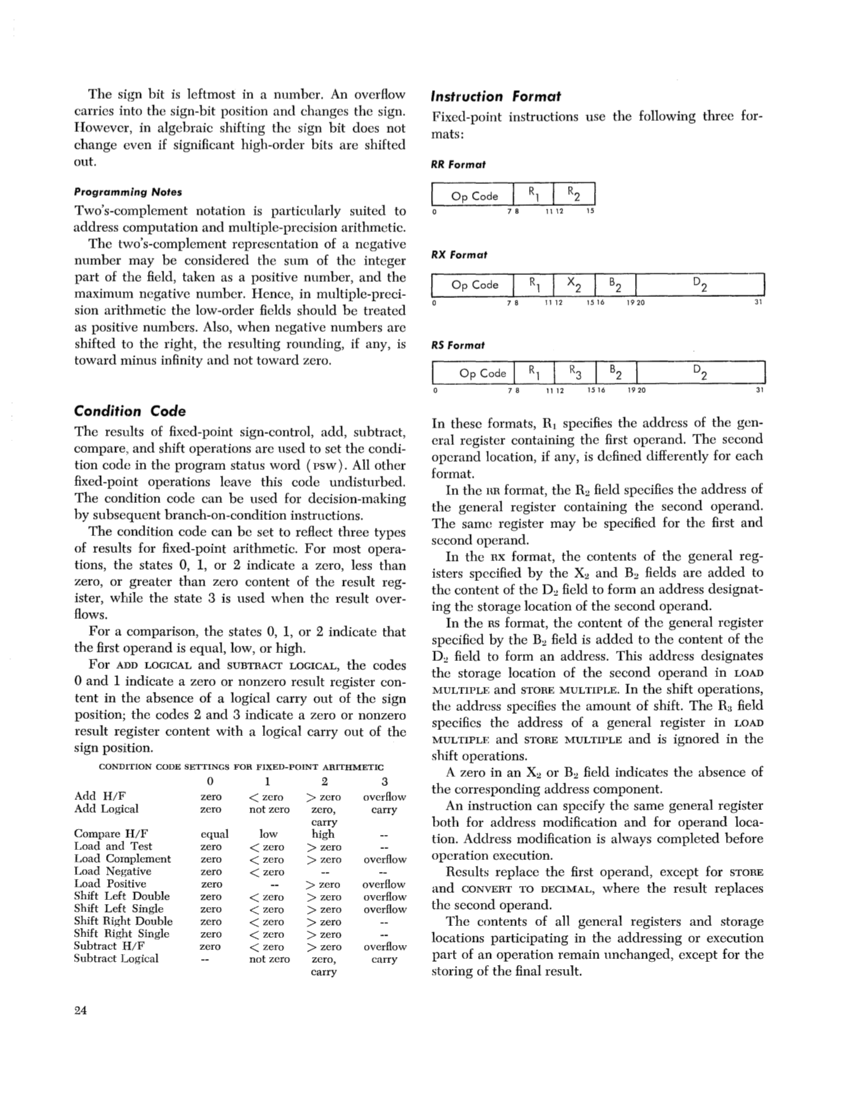

sign position.CONDITION CODE SETTINGS FOR FIXED-POINT ARITHMETIC 0 1 2 3

Add H/F zero < zero > zero overflow

Add Logical zero not zero zero, carry

carryCompare H/F equal low high

Load and Test zero < zero > zero

Load Complement zero < zero > zero overflow

Load Negative zero < zero

Load Positive zero > zero overflow

ShiftLeft Double zero < zero > zero overflow

ShiftLeft Single zero < zero > zero overflow

Shift Right Double zero < zero > zero

Shift Right Single zero < zero > zero

Subtract H/F zero < zero > zero overflow

Subtract Logical not zero zero, carry

carry

24

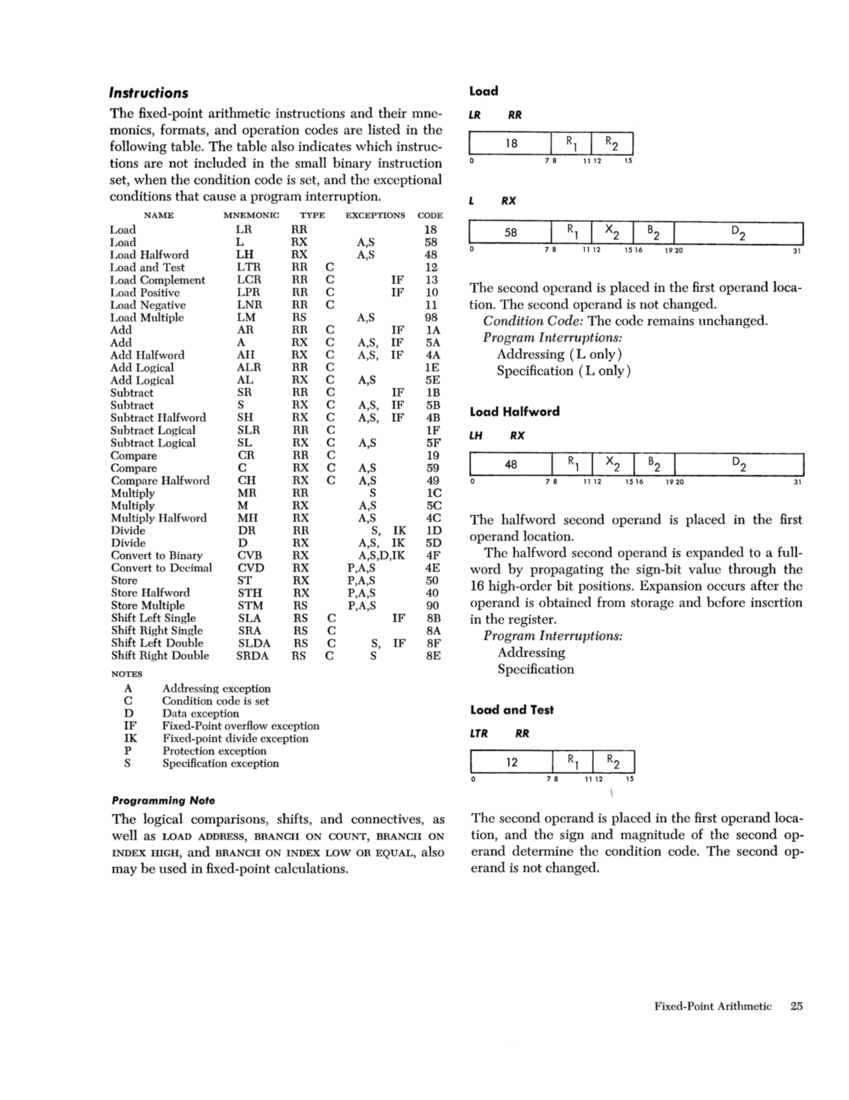

Instruction Format

Fixed-point instructions use the following three for

mats:

RR Format

7 8 11 12 15

RX FormatI Op Code Rl

X

2

B20 7 8 11 12 1516 1920 31

RS FormatOp Code Rl R3 B2

7 8 11 12 1516 1920 31

In these formats, RJ specifies the address of the gen

eral register containing the first operand. The second

operand location, if any, is defined differently for each

format.

In the HR format, theR2 field specifies the address of

the general register containing the second operand.

The same register may be specified for the first and

second operand.

In the RX format, the contents of the general reg

isters specified by theX 2 and B2 fields are added to

the content of theD2 field to form an address designat

ing the storage location of the second operand.

In theRS format, the content of the general register

specified by theB2 field is added to the content of the

D.) field to form an address. This address designatesLOAD MULTIPLE and STORE MULTIPLE. In the shift operations,

the address specifies the amount of shift. The

specifics the address of a general register inLOAD MULTIPLE and STORE MULTIPLE and is ignored in the

shift operations.

A zero in anX 2 or B2 field indicates the absence of

the corresponding address component.

An instruction can specify the same general register

both for address modification and for operand loca

tion. Address modification is always completed before

operation execution.

Results replace the first operand, except forSTORE and CONVERT TO DECIMAL, where the result replaces

the second operand.

The contents of all general registers and storage

locations participating in the addressing or execution

part of an operation remain unchanged, except for the

storing of the final result.

carries into the sign-bit position

However, in algebraic shifting the sign bit does not

change even if significant high-order bits are shifted

out.

Programming Notes

Two's-complement notation is particularly suited to

address computation and multiple-precision arithmetic.

The two's-complement representation of a negative

number may be considered the sum of the integer

part of the field, taken as a positive number, and the

maximum negative number. Hence, in multiple-preci

sion arithmetic the low-order fields should be treated

as positive numbers. Also, when negative numbers are

shifted to the right, the resulting rounding, if any, is

toward minus infinity and not toward zero.

Conditic)n Code

The results of fixed-point sign-control, add, subtract,

tion code in the program status word (psw). All other

fixed-point operations leave this code undisturbed.

The condition code can be used for decision-making

by subsequent branch-on-condition instructions.

The condition code can be set to reHect three types

of results for fixed-point arithmetic. For most opera

tions, the states

zero, or greater than zero content of the result reg

ister' while the state 3 is used when the result over

Hows.

For a comparison, the states

the first operand is equal, low, or high.

For ADD

tent in the absence of a logical carry out of thc sign

position; the codes 2 and 3 indicate a zero or nonzero

result register content with a logical carry out of the

sign position.

Add H/F zero < zero > zero overflow

Add Logical zero not zero zero, carry

carry

Load and Test zero < zero > zero

Load Complement zero < zero > zero overflow

Load Negative zero < zero

Load Positive zero > zero overflow

Shift

Shift

Shift Right Double zero < zero > zero

Shift Right Single zero < zero > zero

Subtract H/F zero < zero > zero overflow

Subtract Logical not zero zero, carry

carry

24

Instruction Format

Fixed-point instructions use the following three for

mats:

RR Format

7 8 11 12 15

RX Format

X

2

B2

RS Format

7 8 11 12 1516 1920 31

In these formats, RJ specifies the address of the gen

eral register containing the first operand. The second

operand location, if any, is defined differently for each

format.

In the HR format, the

the general register containing the second operand.

The same register may be specified for the first and

second operand.

In the RX format, the contents of the general reg

isters specified by the

the content of the

ing the storage location of the second operand.

In the

specified by the

D.) field to form an address. This address designates

the address specifies the amount of shift. The

specifics the address of a general register in

shift operations.

A zero in an

the corresponding address component.

An instruction can specify the same general register

both for address modification and for operand loca

tion. Address modification is always completed before

operation execution.

Results replace the first operand, except for

the second operand.

The contents of all general registers and storage

locations participating in the addressing or execution

part of an operation remain unchanged, except for the

storing of the final result.