The second operand occupies e;ght bytes in storage and has the format of packed

decimal data, asdescribed in Chapter 8, "Decimal Instructions." It is checked

for validsign and digit codes, and a

data exception is recognized when an

invalid code is detected.

The result of the conversion is a 32-bit

signed binary integer, whichis placed in general register R t • The maximum

positive number that canbe converted

and stillbe contained in a 32-bit

register is 2,147,483,647; the maximum

negative number (the negative number

with the greatest absolute value) that

can be converted is -2,147,483,648. For

any decimal number outside this range,

the operation is completed by placing

the 32 rightmost bits of the binary

resultin the register, and a fixed

point-divide exception is recognized.Condition Code: unchanged.

The code remains

Program Exceptions:

Access (fetch, operand 2)

Data

Fixed-point divide

Programming Notes

1. An example of the use of theCONVERT TO BINARY instruction is

given in Appendix A.

2. When the second operand is

negative, the result is in two's

complement notation.

3. The storage-operand references forCONVERT TO BINARY may be multiple

access references.(See the

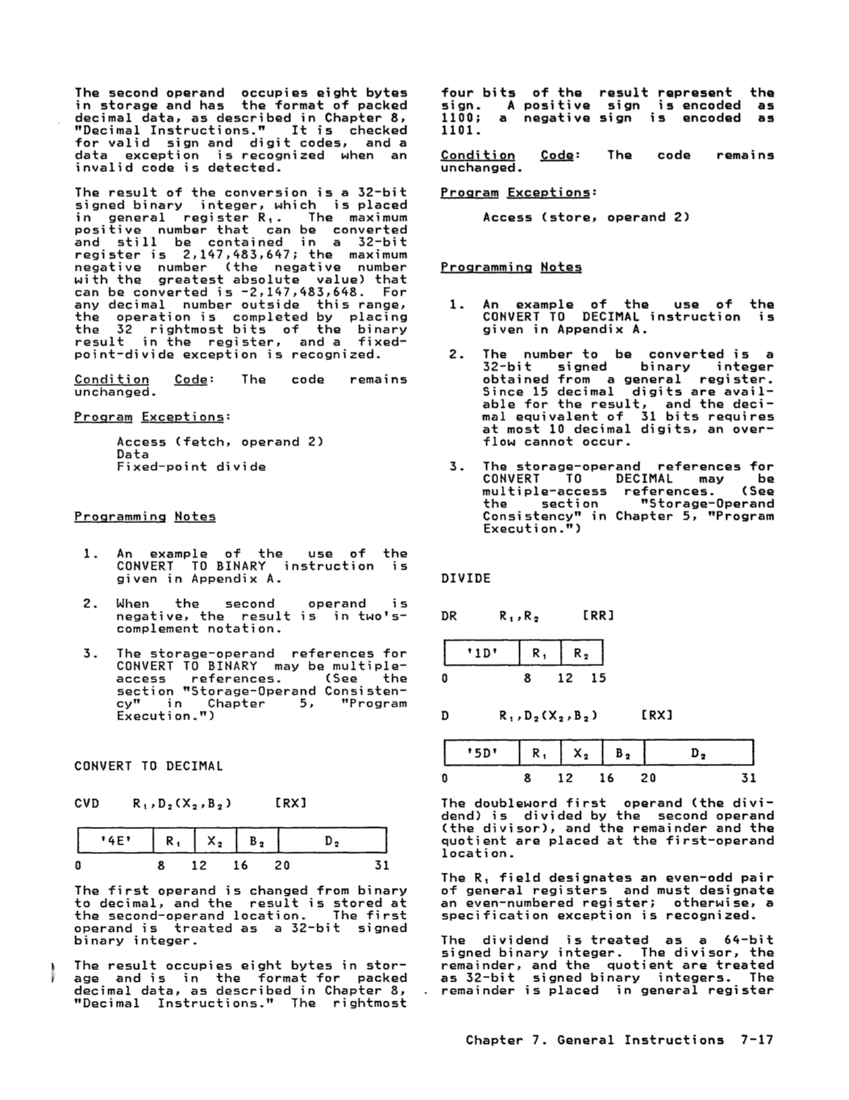

section "Storage-Operand Consistency" in Chapter 5, "Program Execution.") CONVERT TO DECIMAL o 8 12 16 20 31

The first operandis changed from binary

to decimal, and the result is stored at

the second-operand location. The first

operand is treated as a32-bit signed

binary integer.

The result occupies eight bytes in stor

age and is 1n the format for packed

decimal data, as described inChapter 8, "Decimal Instructions." The rightmost

four bits of the result representthe sign. A positive sign ;s encoded as 1100; a negative sign is encoded as 1101. Condition Code: unchanged.

The code remains

Program Exceptions:

Access (store, operand 2)

Programming Notes

1. An example of the use ofthe CONVERT TO DECIMAL instruction is

given in Appendix A.

2. The number to be converted isa 32-bit signed binary integer obtained from a general register. Since 15 decimal digits are avail

able for the result, and thedeci mal equivalent of 31 bits requires

at most10 decimal digits, an over

flow cannot occur.

3. The storage-operand references forCONVERT TO DECIMAL may be

multiple-access references. (See

the section"Storage-Operand Consistency" in Chapter 5, "Program Execution.") DIVIDE

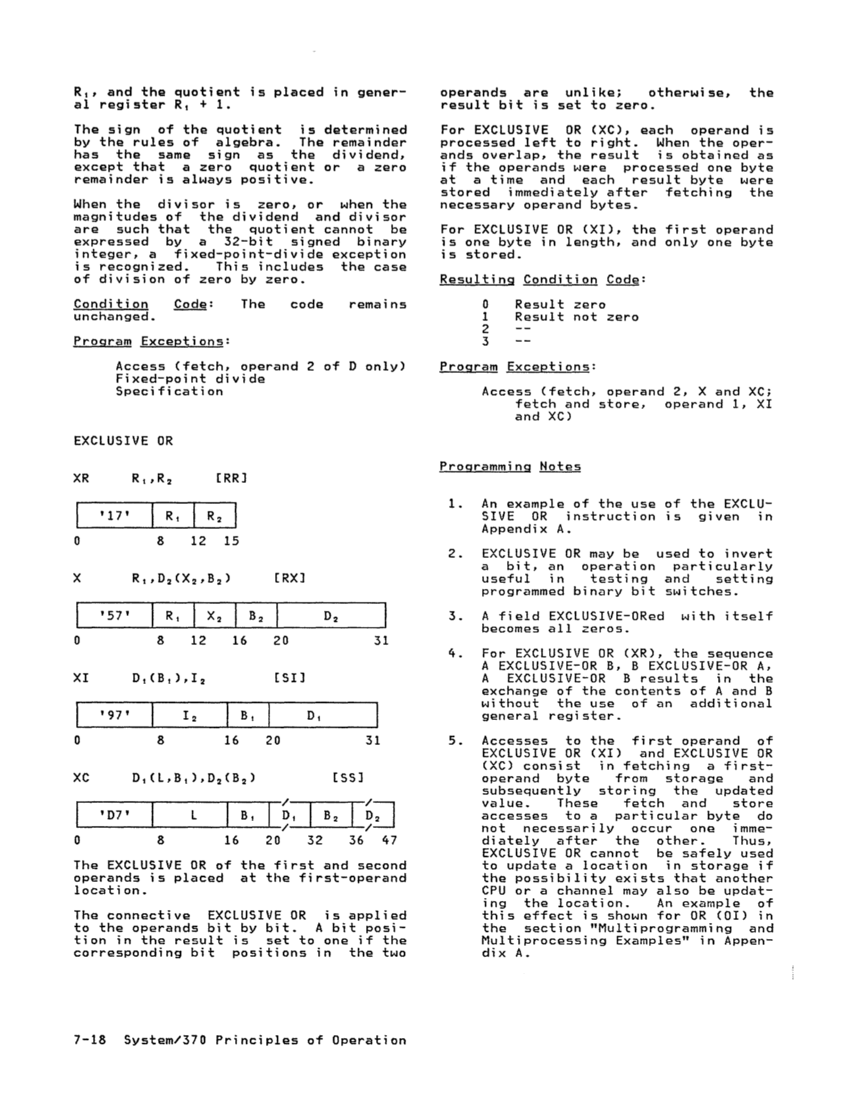

DRR t , R2 [RRl '10' I R t I R2 I 0 8 12 15 0 R

t

,D

2

(X

2

,B

2

) [RXl'50 ' I R t I X 2 I B2 O

2 0 8 12 16 20 31

The doubleword first operand (the divi

dend) is divided by the second operand

(the divisor), and the remainder and the

quotient are placed at the first-operand

location.

The Rt field designates an even-odd pair

of general registers and must designate

an even-numbered register; otherwise, a

specification exception is recognized.

The dividend is treated as a 64-bit

signed binary integer. The divisor, theremainder, and the quotient are treated

as 32-bit signed binary integers. The

remainderis placed in general register Chapter 7. General Instructions 7-17

decimal data, as

for valid

data exception is recognized when an

invalid code is detected.

The result of the conversion is a 32-bit

signed binary integer, which

positive number that can

and still

register is 2,147,483,647; the maximum

negative number (the negative number

with the greatest absolute value) that

can be converted is -2,147,483,648. For

any decimal number outside this range,

the operation is completed by placing

the 32 rightmost bits of the binary

result

point-divide exception is recognized.

The code remains

Program Exceptions:

Access (fetch, operand 2)

Data

Fixed-point divide

Programming Notes

1. An example of the use of the

given in Appendix A.

2. When the second operand is

negative, the result is in two's

complement notation.

3. The storage-operand references for

access references.

section "Storage-Operand Consisten

The first operand

to decimal, and the result is stored at

the second-operand location. The first

operand is treated as a

binary integer.

The result occupies eight bytes in stor

age and is 1n the format for packed

decimal data, as described in

four bits of the result represent

The code remains

Program Exceptions:

Access (store, operand 2)

Programming Notes

1. An example of the use of

given in Appendix A.

2. The number to be converted is

able for the result, and the

at most

flow cannot occur.

3. The storage-operand references for

multiple-access references. (See

the section

DR

t

,D

2

(X

2

,B

2

) [RXl

2

The doubleword first operand (the divi

dend) is divided by the second operand

(the divisor), and the remainder and the

quotient are placed at the first-operand

location.

The Rt field designates an even-odd pair

of general registers and must designate

an even-numbered register; otherwise, a

specification exception is recognized.

The dividend is treated as a 64-bit

signed binary integer. The divisor, the

as 32-bit signed binary integers. The

remainder